LH52256CH Overview

Key Specifications

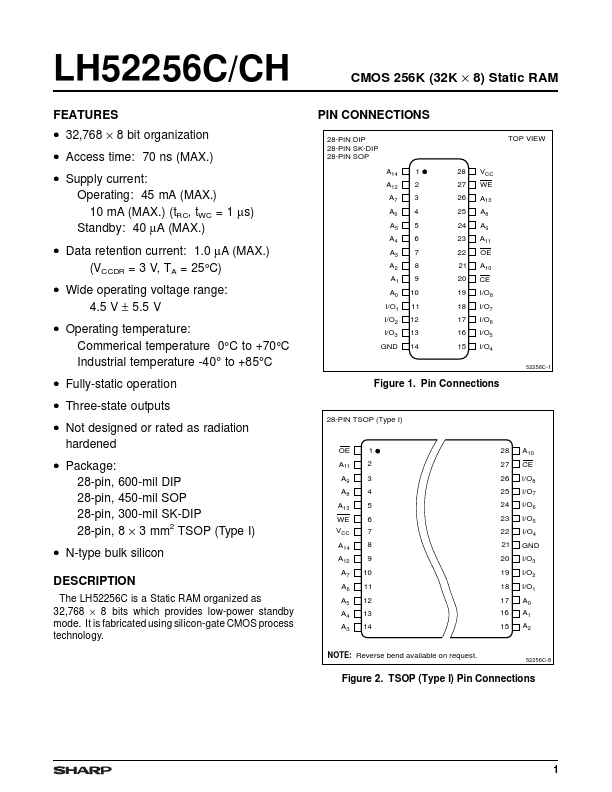

Package: SOP

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Key Features

- 32,768 × 8 bit organization

- Access time: 70 ns (MAX.)

- Supply current: Operating: 45 mA (MAX.) 10 mA (MAX.) (tRC, tWC = 1 µs) Standby: 40 µA (MAX.)

- Data retention current: 1.0 µA (MAX.) (VCCDR = 3 V, TA = 25 °C)

- Wide operating voltage range: 4.5 V ± 5.5 V