LH532100B-1

Key Features

- 262,144 words × 8 bit organization

- Access time: 120 ns (MAX.)

- Static operation

- TTL compatible I/O

- Three-state outputs

- Single +5 V power supply

- Power consumption: Operating: 275 mW (MAX.) Standby: 550 µW (MAX.)

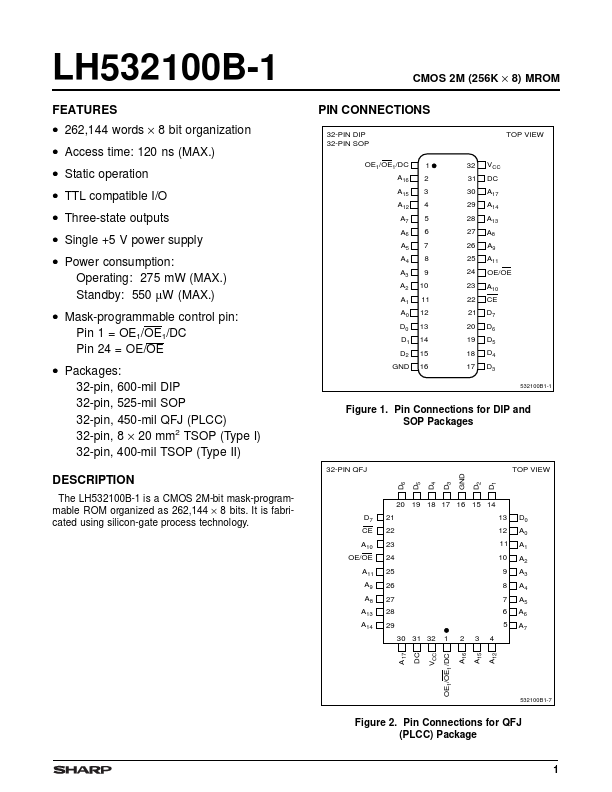

- Mask-programmable control pin: Pin 1 = OE1/OE1/DC Pin 24 = OE/OE

- Packages: 32-pin, 600-mil DIP 32-pin, 525-mil SOP 32-pin, 450-mil QFJ (PLCC) 32-pin, 8 × 20 mm2 TSOP (Type I) 32-pin, 400-mil TSOP (Type II) DESCRIPTION The LH532100B-1 is a CMOS 2M-bit mask-programmable ROM organized as 262,144 × 8 bits. It is fabricated using silicon-gate process technology.