LH5P8129

Key Features

- 131,072 × 8 bit organization

- Access times (MAX.): 60/80/100 ns

- Cycle times (MIN.): 100/130/160 ns

- Single +5 V power supply

- Pin compatible with 1M standard SRAM

- Power consumption: Operating: 572/385/275 mW (MAX.) Standby (TTL level): 5.5 mW (MAX.) Standby (CMOS level): 1.1 mW (MAX.)

- TTL compatible I/O

- Available for auto-refresh and self-refresh modes

- 512 refresh cycles/8 ms

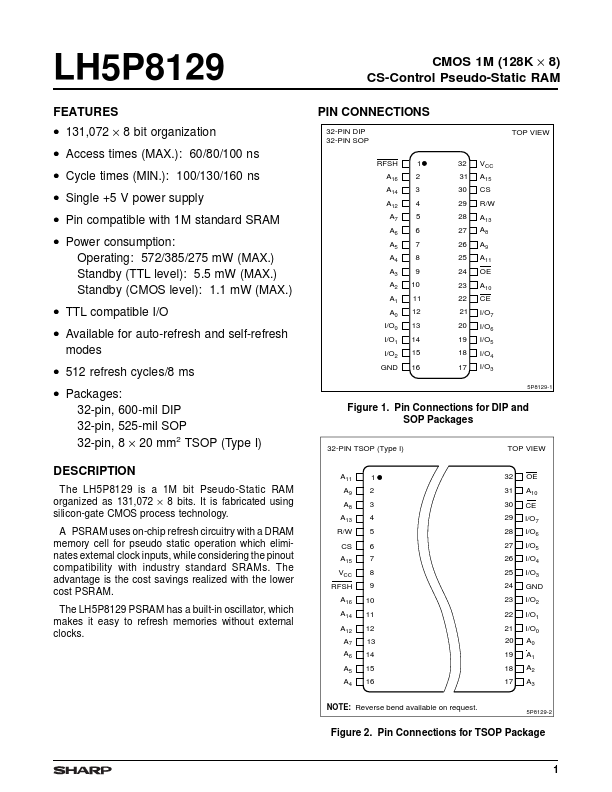

- Packages: 32-pin, 600-mil DIP 32-pin, 525-mil SOP 32-pin, 8 × 20 mm2 TSOP (Type I) DESCRIPTION The LH5P8129 is a 1M bit Pseudo-Static RAM organized as 131,072 × 8 bits. It is fabricated using silicon-gate CMOS process technology. A PSRAM uses on-chip refresh circuitry with a DRAM memory cell for pseudo static operation which eliminates external clock inputs, while considering the pinout compatibility with industry standard SRAMs. The advantage is the cost savings realized with the lower cost PSRAM. The LH5P8129 PSRAM has a built-in oscillator, which makes it easy to refresh memories without external clocks.