LH28F008SA

LH28F008SA is 8M (1M x 8) Flash Memory manufactured by Sharp Corporation.

Features

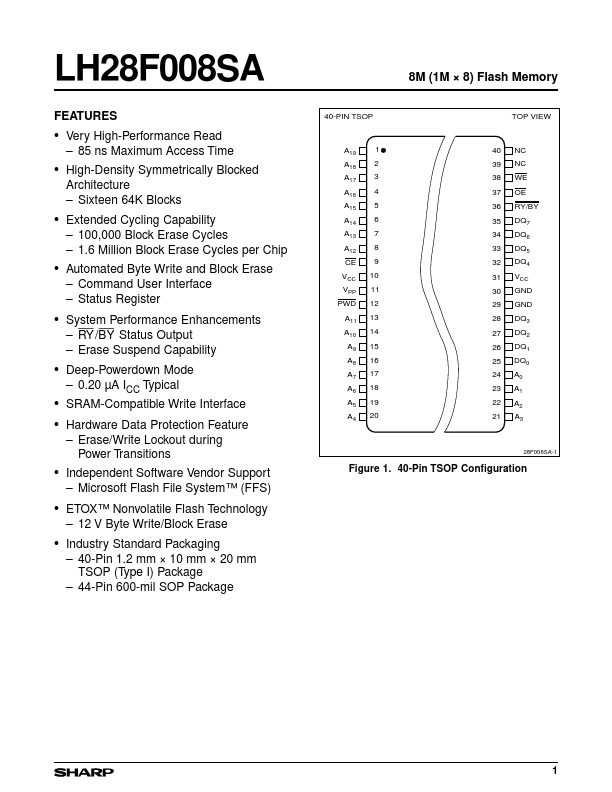

40-PIN TSOP

8M (1M × 8) Flash Memory

TOP VIEW

- Very High-Performance Read

- 85 ns Maximum Access Time

A19 A18 A17 A16 A15 A14 A13 A12 CE VCC VPP PWD A11 A10 A9 A8 A7 A6 A5 A4 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 NC NC WE OE RY/BY DQ7 DQ6 DQ5 DQ4 VCC GND GND DQ3 DQ2 DQ1 DQ0 A0 A1 A2 A3

- High-Density Symmetrically Blocked

Architecture

- Sixteen 64K Blocks

- Extended Cycling Capability

- 100,000 Block Erase Cycles

- 1.6 Million Block Erase Cycles per Chip

- Automated Byte Write and Block Erase

- mand User Interface

- Status Register

- System Performance Enhancements

- RY / » BY » Status...