Si5384

Si5384 is Network Synchronizer Clocks Supporting manufactured by Silicon Labs.

- Part of the Si5383 comparator family.

- Part of the Si5383 comparator family.

FEATURES

- One or three independent DSPLLs in a single monolithic IC supporting flexible Sync E/IEEE 1588 and SETS architectures

- Input frequency range:

- External crystal: 25-54 MHz

- REF clock: 5-250 MHz

- Diff clock: 8 k Hz

- 750 MHz

- LVCMOS clock: 1 PPS, 8 k Hz

- 250 MHz

- Output frequency range:

- Differential: 1 PPS, 100 Hz

- 718.5 MHz

- LVCMOS: 1 PPS, 100 Hz

- 250 MHz

- Ultra-low jitter of less than 150 fs

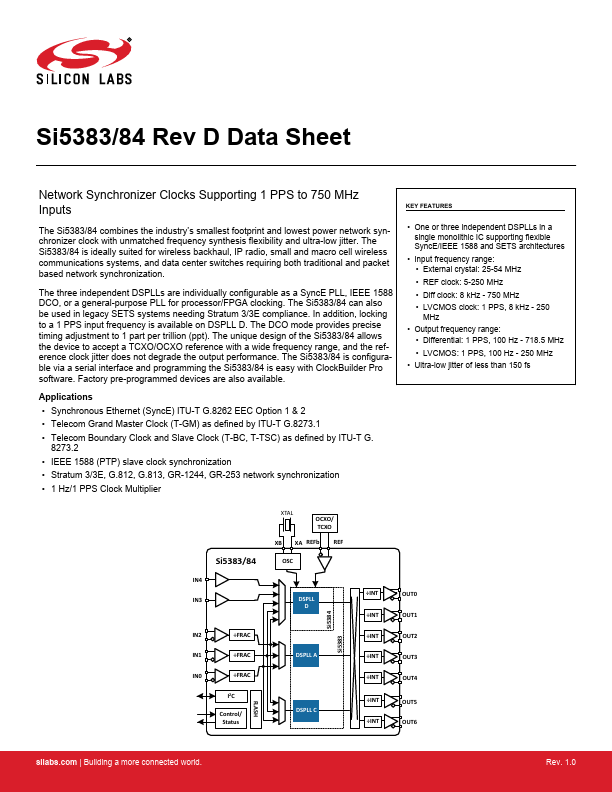

Si5383/84

IN4 IN3

XTAL OCXO/ TCXO

XB XA REFb REF OSC

DSPLL D

IN2

÷FRAC

IN1

÷FRAC

IN0

÷FRAC

I2C Control/ Status

FLASH

DSPLL A DSPLL C

Si5384 Si5383

÷INT ÷INT ÷INT ÷INT ÷INT ÷INT ÷INT

OUT0 OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 silabs. | Building a more connected world.

Rev. 1.0

Table of Contents

1. Feature

List

- -

- -

- - . . 1

2. Ordering...