Si53361 Overview

Key Specifications

Operating Voltage: 1.8 V

Max Voltage (typical range): 1.89 V

Min Voltage (typical range): 1.71 V

Length: 3 mm

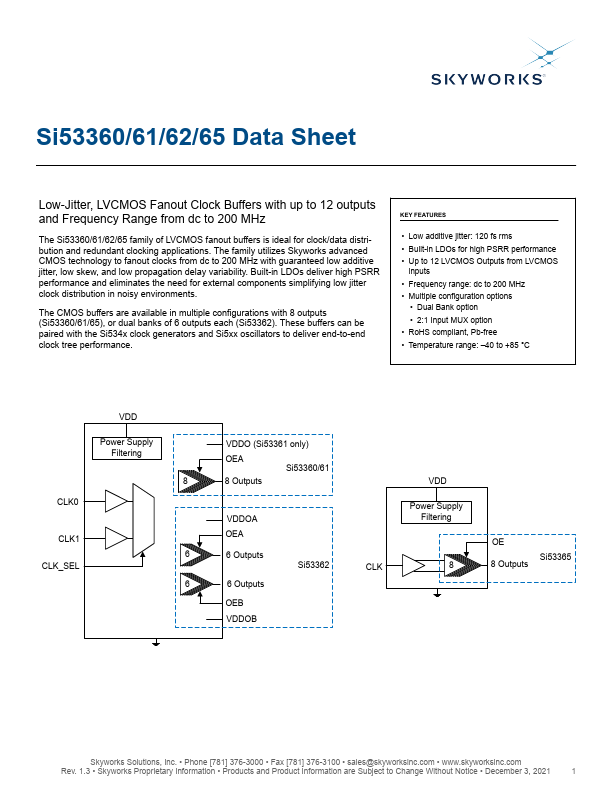

Key Features

- Low additive jitter: 120 fs rms

- Built-in LDOs for high PSRR performance

- Up to 12 LVCMOS Outputs from LVCMOS inputs

- Frequency range: dc to 200 MHz

- Multiple configuration options