Si53365

Overview

- Low additive jitter: 120 fs rms

- Built-in LDOs for high PSRR performance

- Up to 12 LVCMOS Outputs from LVCMOS inputs

- Frequency range: dc to 200 MHz

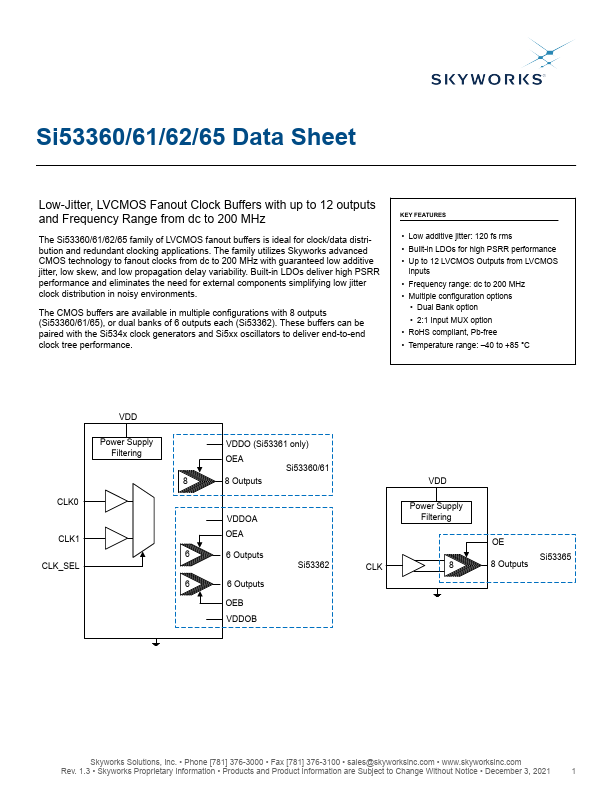

- Multiple configuration options

- Dual Bank option

- 2:1 Input MUX option

- RoHS compliant, Pb-free

- Temperature range: -40 to +85 °C VDD Power Supply Filtering CLK0 8 0 CLK1 CLK_SEL 1 6 6 VDDO (Si53361 only) OEA 8 Outputs Si53360/61