CXL5512M

CXL5512M is CMOS-CCD 1H Delay Line for NTSC manufactured by Sony Semiconductor Solutions.

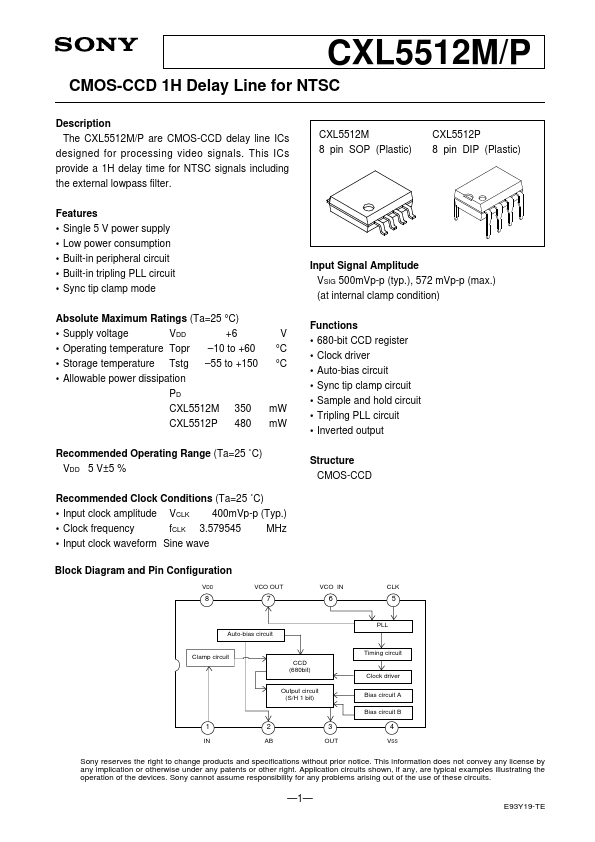

CXL5512M/P

CMOS-CCD 1H Delay Line for NTSC

Description The CXL5512M/P are CMOS-CCD delay line ICs designed for processing video signals. This ICs provide a 1H delay time for NTSC signals including the external lowpass filter. Features

- Single 5 V power supply

- Low power consumption

- Built-in peripheral circuit

- Built-in tripling PLL circuit

- Sync tip clamp mode...