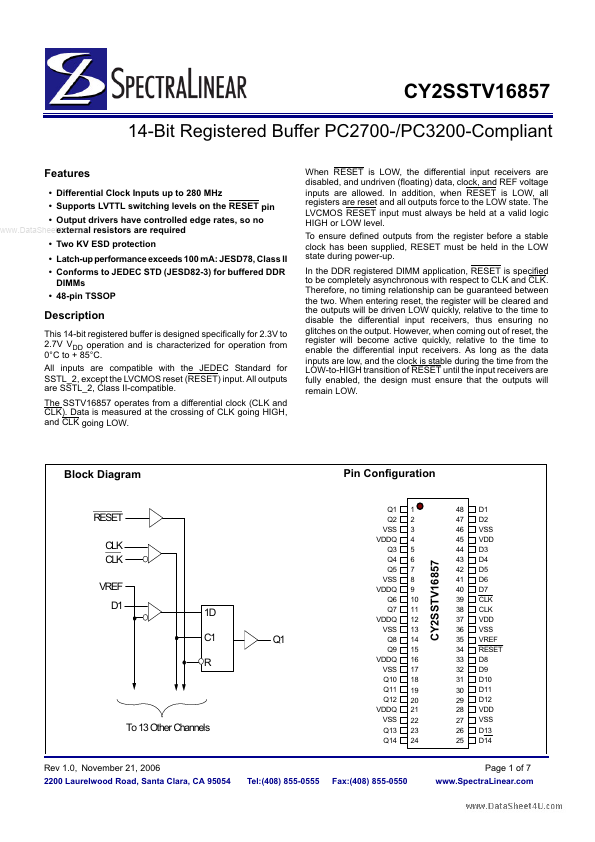

CY2SSTV16857 Description

This 14-bit registered buffer is designed specifically for 2.3V to 2.7V VDD operation and is characterized for operation from 0°C to + 85°C. All inputs are patible with the JEDEC Standard for SSTL_2, except the LVCMOS reset (RESET) input. All outputs are SSTL_2, Class II-patible.

CY2SSTV16857 Key Features

- Differential Clock Inputs up to 280 MHz

- Supports LVTTL switching levels on the RESET pin

- Output drivers have controlled edge rates, so no .. external resistors are required

- Two KV ESD protection

- Latch-up performance exceeds 100 mA: JESD78, Class II

- Conforms to JEDEC STD (JESD82-3) for buffered DDR DIMMs

- 48-pin TSSOP When RESET is LOW, the differential input receivers are disabled, and undriven (floating) data, clock, and