TD72403L10DB

Key Features

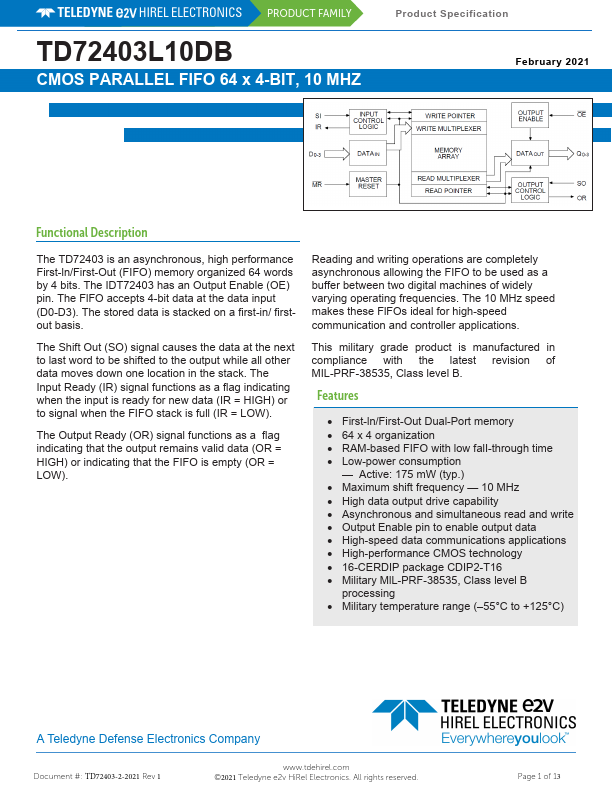

- First-ln/First-Out Dual-Port memory

- 64 x 4 organization

- RAM-based FIFO with low falI-through time

- Low-power consumption

- Active: 175 mW (typ.)

- Maximum shift frequency - 10 MHz

- High data output drive capability

- Asynchronous and simultaneous read and write

- Output Enable pin to enable output data

- High-speed data munications applications