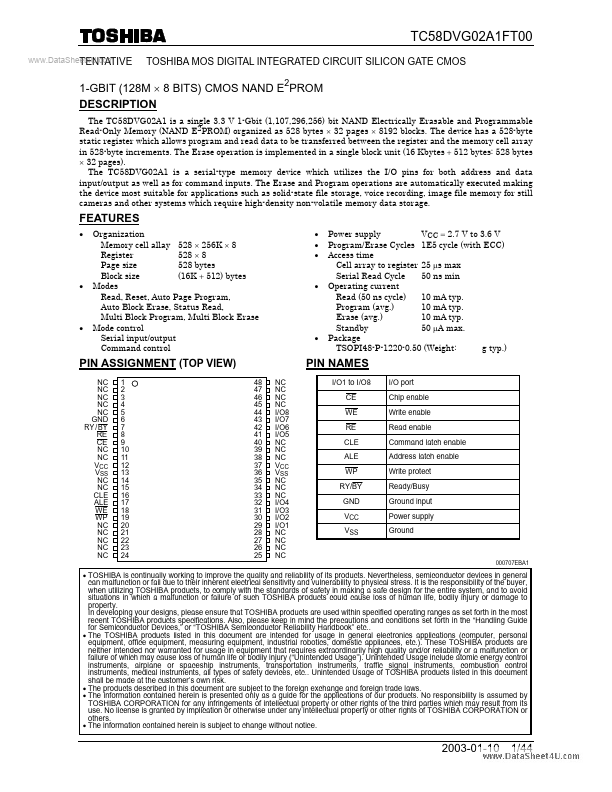

| Part | TC58DVG02A1FT00 |

|---|---|

| Description | MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS |

| Manufacturer | Toshiba |

| Size | 511.12 KB |

Pricing from 1.8893 USD, available from Worldway Electronics and IC Components Ltd..

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Worldway Electronics | 24958 | 7+ : 1.8893 USD 10+ : 1.8515 USD 100+ : 1.7948 USD 500+ : 1.7382 USD |

View Offer |

| IC Components Ltd. | 2422 | - | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| OV3660 | Ommivision | color CMOS QSXGA image sensor |

| M3727GM6-XXXSP | Renesas | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38749MFT-XXXFS | Mitsubishi Electric | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |