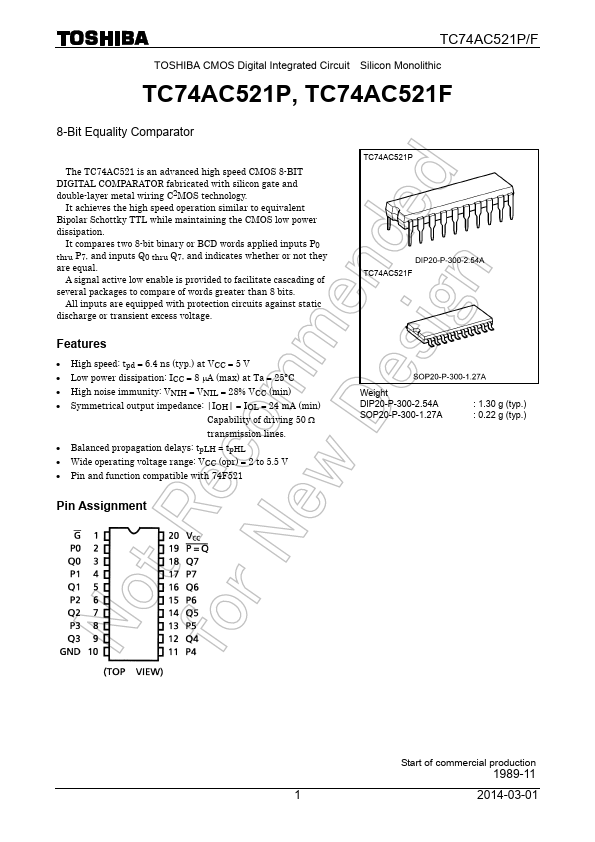

TC74AC521F

TC74AC521F is 8-Bit Equality Comparator manufactured by Toshiba.

TC74AC521P/F

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74AC521P, TC74AC521F

8-Bit Equality parator

The TC74AC521 is an advanced high speed CMOS 8-BIT DIGITAL PARATOR fabricated with silicon gate and double-layer metal wiring C2MOS technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

It pares two 8-bit binary or BCD words applied inputs P0 thru P7, and inputs Q0 thru Q7, and indicates whether or not they are equal.

A signal active low enable is provided to facilitate cascading of several packages to pare of words greater than 8 bits.

All inputs are equipped with...