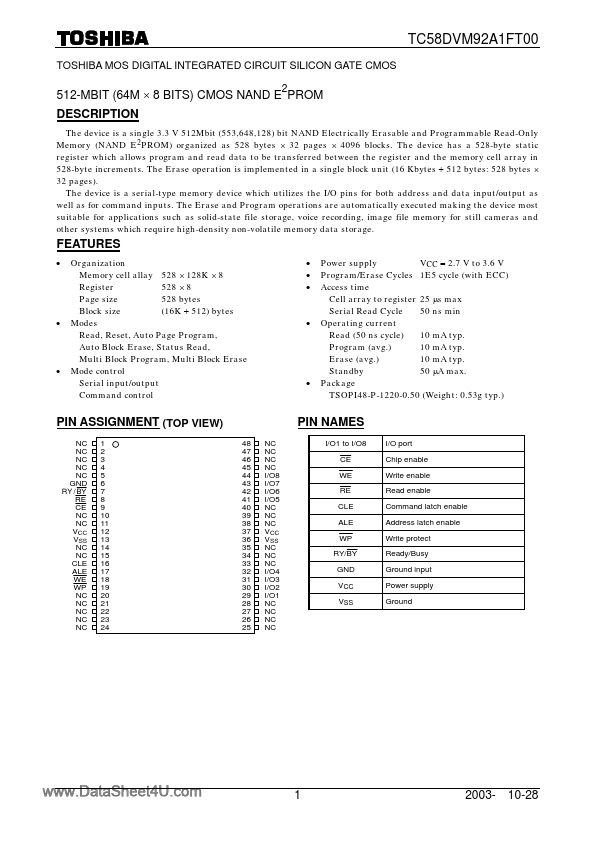

| Part | TC58DVM92A1FT00 |

|---|---|

| Description | 512M-Bit CMOS NAND EPROM |

| Manufacturer | Toshiba |

| Size | 410.61 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CY2081 | Cypress | Three-PLL General-Purpose EPROM-Programmable Clock Generator |

| W27C512 | Winbond | 64K x 8 ELECTRICALLY ERASABLE EPROM |

| M27C256B | STMicroelectronics | 256 Kbit (32Kb x 8) UV EPROM and OTP EPROM |