TC74HC4024AF

TC74HC4024AF is 7-Stage Binary Counter manufactured by Toshiba.

- Part of the TC74HC4024AP comparator family.

- Part of the TC74HC4024AP comparator family.

TC74HC4024AP/AF

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74HC4024AP, TC74HC4024AF

7-Stage Binary Counter

The TC74HC4024A is a high speed CMOS 7-STAGE BINARY COUNTER fabricated with silicon gate C2MOS technology.

It achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation.

A negative transition on the CK input brings one increment to the counter.

A CLR input is used to reset the counter to the all low level state. A high level at CLR acplishes the reset function.

All divided output stages are provided, and the last stage, 1/128 divided frequency will be obtained.

All inputs are equipped with protection circuits against static discharge or transient excess voltage.

Features

- High speed: fmax = 70 MHz (typ.) at VCC = 5 V

- Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Output drive capability: 10 LSTTL loads

- Symmetrical output impedance: |IOH| = IOL = 4 m A (min)

- Balanced propagation delays: tp LH ∼- tp HL

- Wide operating voltage range: VCC (opr) = 2 to 6 V

- Pin and function patible with 4024B

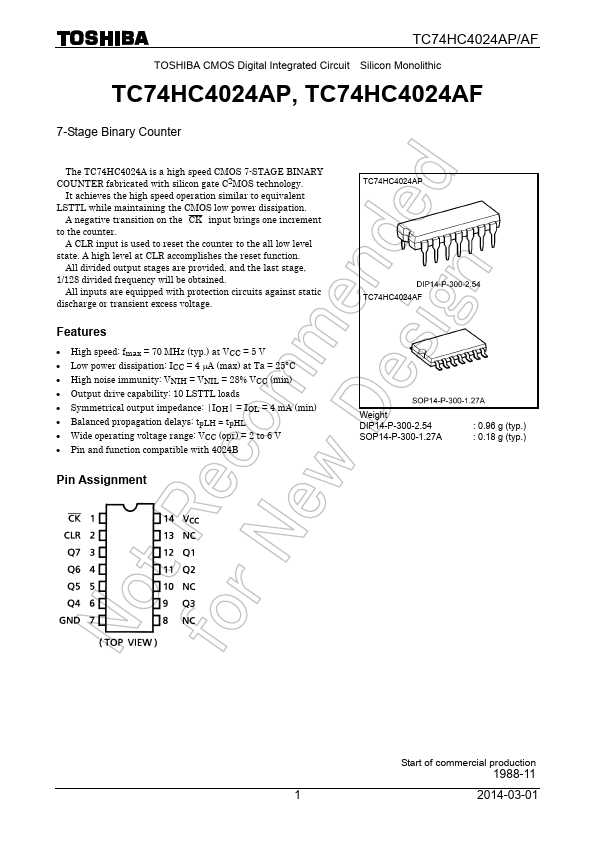

Pin Assignment

TC74HC4024AP

Weight DIP14-P-300-2.54 SOP14-P-300-1.27A

: 0.96 g (typ.) : 0.18 g (typ.)

Start of mercial production

1988-11

2014-03-01

IEC Logic Symbol

Truth Table

Inputs

CK...