TC74HC4028AF

TC74HC4028AF is BCD-to-Decimal Decoder manufactured by Toshiba.

- Part of the TC74HC4028AP comparator family.

- Part of the TC74HC4028AP comparator family.

TC74HC4028AP/AF

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74HC4028AP, TC74HC4028AF

BCD-to-Decimal Decoder

The TC74HC4028A is a high speed CMOS BCD-to-DECIMAL DECODER fabricated with silicon gate C2MOS technology.

It achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation.

A BCD code applied to the four inputs (A-D) sets a high level at one of ten decoded outputs. A illegal BCD code such as eleven thru fifteen sets all outputs low. This device can be used as 3-to-8 LINE DECODER when input D is held high.

This device is useful for code conversion, address decoding, memory selection, multiplexing, or readout decoding.

All inputs are equipped with protection circuits against static discharge or transient excess voltage.

Features

- High speed: tpd = 18 ns (typ.) at VCC = 5 V

- Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Output drive capability: 10 LSTTL loads

- Symmetrical output impedance: |IOH| = IOL = 4 m A (min)

- Balanced propagation delays: tp LH ∼- tp HL

- Wide operating voltage range: VCC (opr) = 2 to 6 V

- Pin and function patible with 4028B.

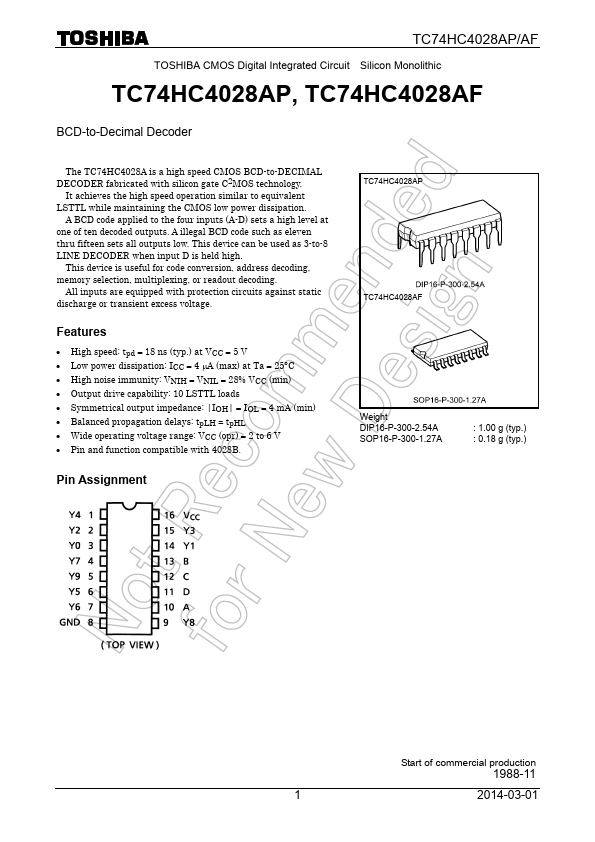

Pin Assignment

TC74HC4028AP

Weight DIP16-P-300-2.54A SOP16-P-300-1.27A

: 1.00 g (typ.) : 0.18 g (typ.)

Start of mercial production

1988-11

2014-03-01

IEC Logic Symbol

TC74HC4028AP/AF

Truth Table

Inputs

X: Don’t...