TC74VHC373FW

TC74VHC373FW is OCTAL D-TYPE LATCH WITH 3-STATE OUTPUT manufactured by Toshiba.

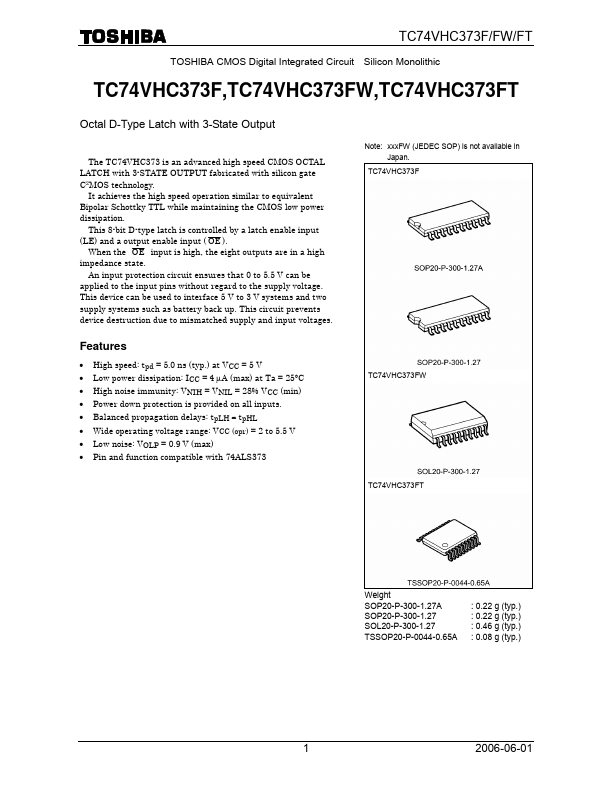

TC74VHC373F/FW/FT

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74VHC373F,TC74VHC373FW,TC74VHC373FT

Octal D-Type Latch with 3-State Output

The TC74VHC373 is an advanced high speed CMOS OCTAL LATCH with 3-STATE OUTPUT fabricated with silicon gate C2MOS technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

This 8-bit D-type latch is controlled by a latch enable input (LE) and a output enable input ( OE ).

When the OE input is high, the eight outputs are in a high impedance state.

An input protection circuit ensures that 0 to 5.5 V can be applied to the input pins without regard to the...