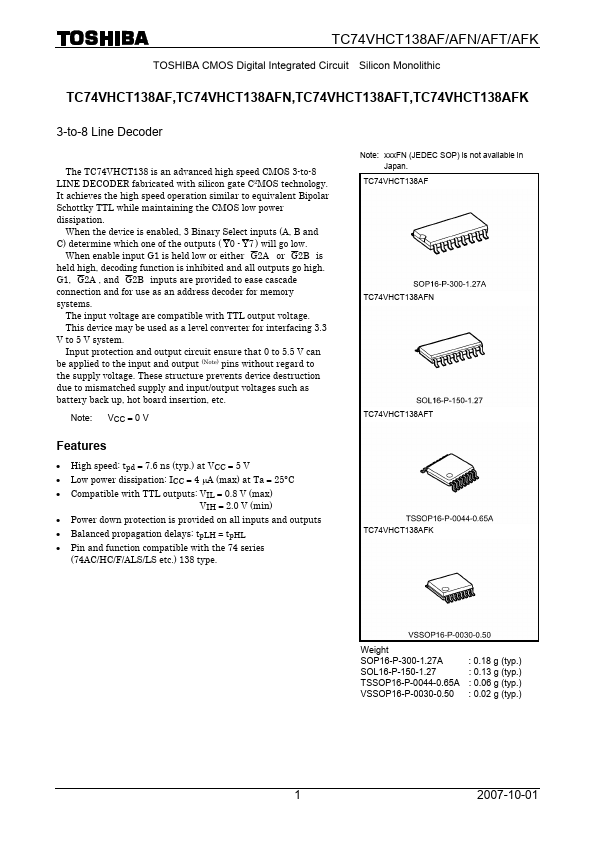

TC74VHCT138AFN

Key Features

- High speed: tpd = 7.6 ns (typ.) at VCC = 5 V

- Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

- Compatible with TTL outputs: VIL = 0.8 V (max) VIH = 2.0 V (min)

- Power down protection is provided on all inputs and outputs

- Balanced propagation delays: tpLH ∼- tpHL

- Pin and function compatible with the 74 series (74AC/HC/F/ALS/LS etc.) 138 type. Note: xxxFN (JEDEC SOP) is not available in Japan.