TXC-05804

TXC-05804 is ATM DATA-LINK SWITCHING/ROUTING manufactured by Transwitch.

..

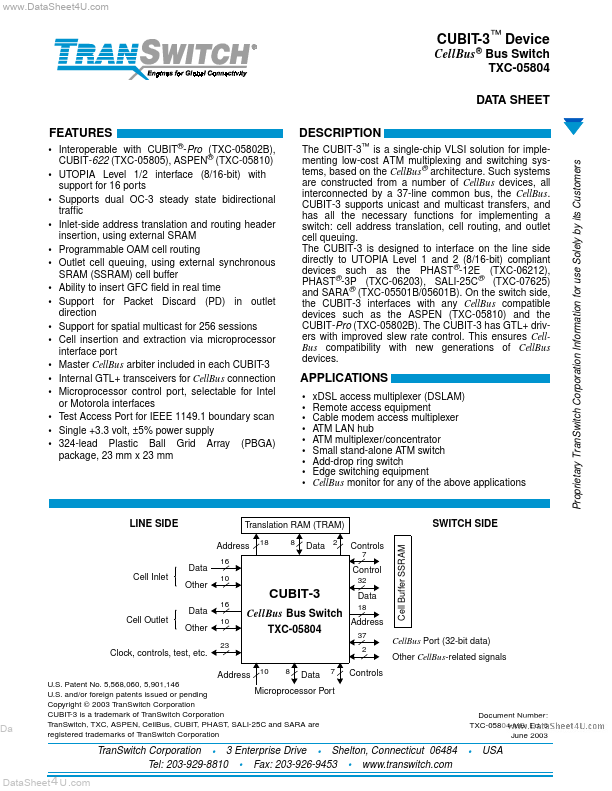

CUBIT-3™ Device

Cell Bus® Bus Switch TXC-05804 DATA SHEET Features

CUBIT®-Pro

DESCRIPTION

Proprietary Tran Switch Corporation Information for use Solely by its Customers

- Interoperable with (TXC-05802B), The CUBIT-3™ is a single-chip VLSI solution for imple® menting low-cost ATM multiplexing and switching sys CUBIT-622 (TXC-05805), ASPEN (TXC-05810) tems, based on the Cell Bus® architecture. Such systems

- UTOPIA Level 1/2 interface (8/16-bit) with are constructed from a number of Cell Bus devices, all support for 16 ports interconnected by a 37-line mon bus, the Cell Bus.

- Supports dual OC-3 steady state bidirectional CUBIT-3 supports unicast and multicast transfers, and traffic has all the necessary functions for implementing a

- Inlet-side address translation and routing header switch: cell address translation, cell routing, and outlet insertion, using external SRAM cell queuing. The CUBIT-3 is designed to interface on the line side

- Programmable OAM cell routing directly to UTOPIA Level 1 and 2 (8/16-bit) pliant

- Outlet cell queuing, using external synchronous devices such as the PHAST®-12E (TXC-06212), SRAM (SSRAM) cell buffer PHAST®-3P (TXC-06203), SALI-25C® (TXC-07625)

- Ability to insert GFC field in real time and SARA® (TXC-05501B/05601B). On the switch side,

- Support for Packet Discard (PD) in outlet the CUBIT-3 interfaces with any Cell Bus patible direction devices such as the ASPEN (TXC-05810) and the CUBIT-Pro (TXC-05802B). The CUBIT-3 has GTL+ driv- Support for spatial multicast for 256 sessions ers with improved slew rate control. This ensures Cell- Cell insertion and extraction via microprocessor Bus patibility with new generations of Cell Bus interface port devices.

- Master Cell Bus arbiter included in each CUBIT-3

- Internal GTL+ transceivers for Cell Bus connection APPLICATIONS

- Microprocessor control port, selectable for Intel .

- x DSL access multiplexer (DSLAM) or Motorola interfaces

- Remote...