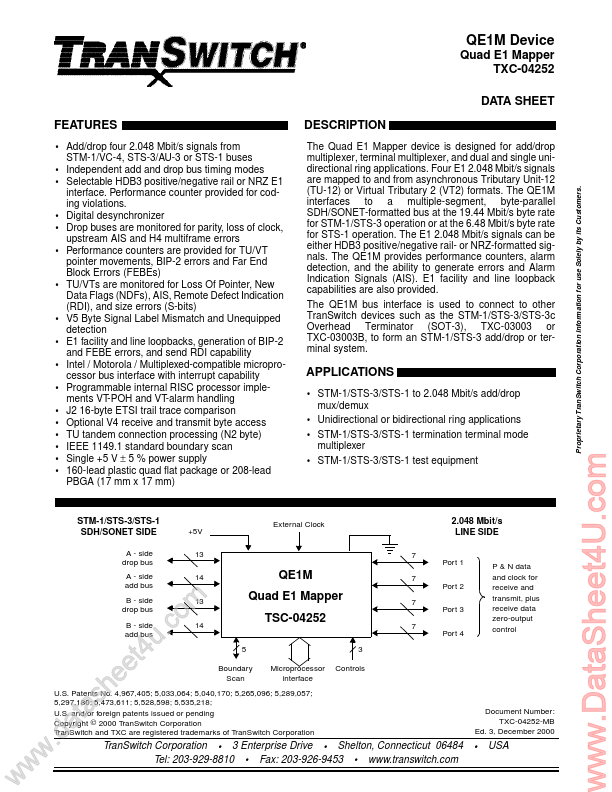

TXC04252

FEATURES

- Add/drop four 2.048 Mbit/s signals from STM-1/VC-4, STS-3/AU-3 or STS-1 buses

- Independent add and drop bus timing modes

- Selectable HDB3 positive/negative rail or NRZ E1 interface. Performance counter provided for coding violations.

- Digital desynchronizer

- Drop buses are monitored for parity, loss of clock, upstream AIS and H4 multiframe errors

- Performance counters are provided for TU/VT pointer movements, BIP-2 errors and Far End Block Errors (FEBEs)

- TU/VTs are monitored for Loss Of Pointer, New Data Flags (NDFs), AIS, Remote Defect Indication (RDI), and size errors (S-bits)

- V5 Byte Signal Label Mismatch and Unequipped detection

- E1 facility and line loopbacks, generation of BIP-2 and FEBE errors, and send RDI capability

- Intel / Motorola / Multiplexed-patible microprocessor bus interface with interrupt capability

- Programmable internal RISC processor implements VT-POH and VT-alarm handling

- J2 16-byte ETSI trail trace parison

- Optional V4 receive and...