TQ1089

TQ1089 is 11-Output Configurable Clock Buffer manufactured by TriQuint Semiconductor.

S E M I C O N D U C T O R, I N C .

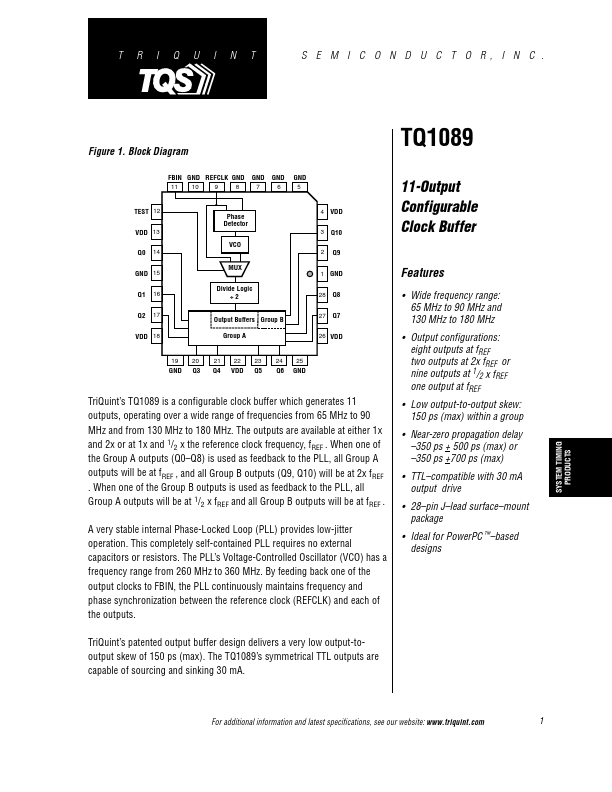

Figure 1. Block Diagram

FBIN GND REFCLK GND GND GND

11 10 9 8 7 6

5 4 VDD 3

TEST 12 VDD 13

Phase Detector VCO

Q10 Q9

11-Output Configurable Clock Buffer

Features

- Wide frequency range: 65 MHz to 90 MHz and 130 MHz to 180 MHz

- Output configurations: eight outputs at fREF two outputs at 2x fREF or nine outputs at 1/2 x fREF one output at fREF

- Low output-to-output skew: 150 ps (max) within a group

SYSTEM TIMING PRODUCTS

Q0

GND 15 Q1 Q2

16 17

MUX Divide Logic ÷2 Output Buffers Group B Group A

1 GND 28 27

Q8 Q7

VDD 18

26 VDD

Q3

Q4

Q5

Q6

TriQuint’s TQ1089...