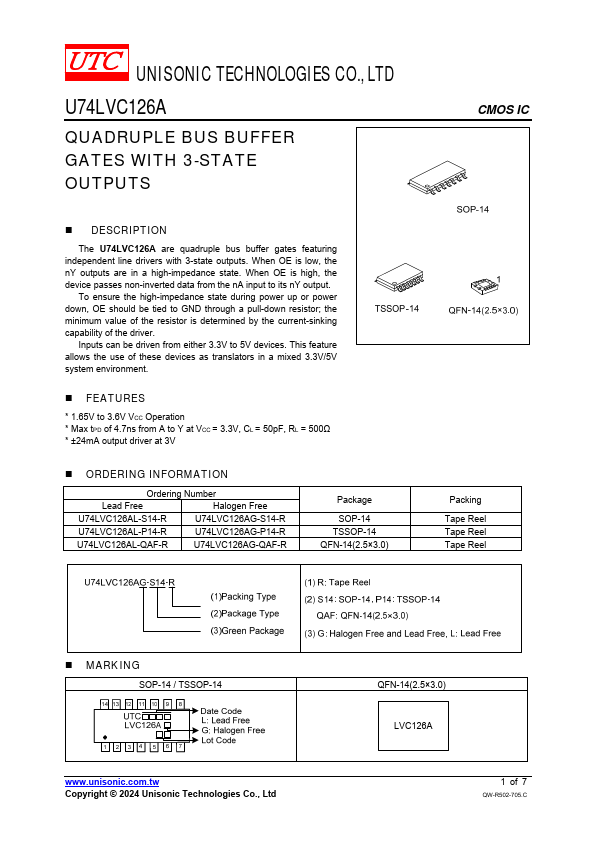

U74LVC126A

U74LVC126A is QUADRUPLE BUS BUFFER GATES manufactured by Unisonic Technologies.

UNISONIC TECHNOLOGIES CO., LTD

QUADRUPLE BUS BUFFER GATES WITH 3-STATE OUTPUTS

- DESCRIPTION

The U74LVC126A are quadruple bus buffer gates featuring independent line drivers with 3-state outputs. When OE is low, the nY outputs are in a high-impedance state. When OE is high, the device passes non-inverted data from the nA input to its nY output.

To ensure the high-impedance state during power up or power down, OE should be tied to GND through a pull-down resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Inputs can be driven from either 3.3V to 5V devices. This feature allows the use of these devices as translators in a...