Datasheet Summary

Overview

Preliminary

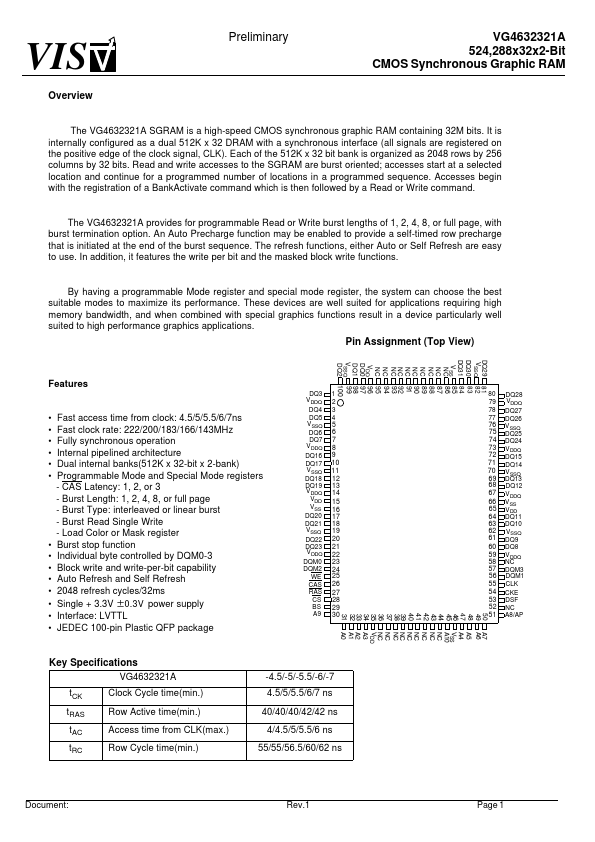

VG4632321A 524,288x32x2-Bit CMOS Synchronous Graphic RAM

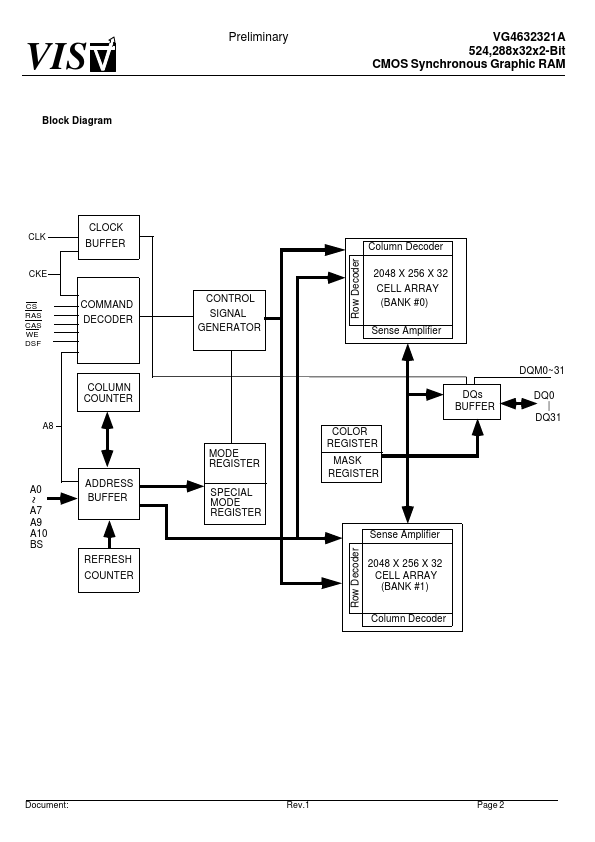

The VG4632321A SGRAM is a high-speed CMOS synchronous graphic RAM containing 32M bits. It is internally configured as a dual 512K x 32 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the 512K x 32 bit bank is organized as 2048 rows by 256 columns by 32 bits. Read and write accesses to the SGRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of a BankActivate mand which is then followed by a Read or Write...