SI1907DL

SI1907DL is Dual P-Channel 1.8-V MOSFET manufactured by Vishay.

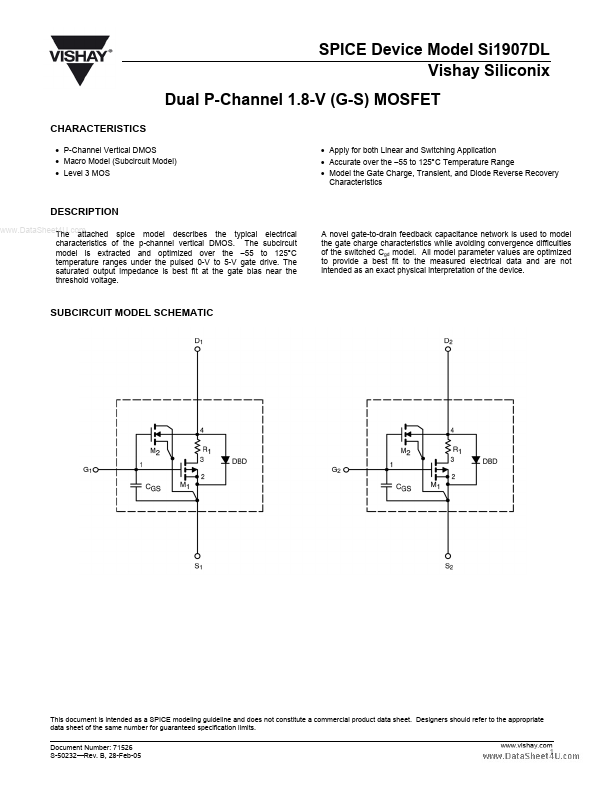

DESCRIPTION

.. The attached spice model describes the typical electrical characteristics of the p-channel vertical DMOS. The subcircuit model is extracted and optimized over the

- 55 to 125°C temperature ranges under the pulsed 0-V to 5-V gate drive. The saturated output impedance is best fit at the gate bias near the threshold voltage.

A novel gate-to-drain feedback capacitance network is used to model the gate charge characteristics while avoiding convergence difficulties of the switched Cgd model. All model parameter values are optimized to provide a best fit to the measured electrical data and are not intended as an exact physical interpretation of the device.

SUBCIRCUIT MODEL SCHEMATIC

This document is intended as a SPICE modeling guideline and does not constitute a mercial product data sheet. Designers should refer to the appropriate data sheet of the same number for guaranteed specification limits. Document Number: 71526 S-50232Rev. B, 28-Feb-05 .vishay. 1

SPICE Device Model Si1907DL Vishay Siliconix

SPECIFICATIONS (TJ = 25°C UNLESS OTHERWISE NOTED) Parameter Static

Gate Threshold Voltage On-State Drain Current a

Symbol

Test Condition

Simulated Data

0.78 5.8 0.54 0.77 1.05 1.19

- 0.76

Measured Data

Unit

VGS(th) ID(on)

VDS = VGS, ID =

- 250 µA VDS =

- 5 V, VGS =

- 4.5 V VGS =

- 4.5 V, ID =

- 0.53 A

V A 0.57 0.80 1.25 1.1

- 0.80 S V Ω

Drain-Source On-State Resistance a r DS(on)

VGS =

- 2.5 V, ID =

- 0.44 A VGS =

- 1.8 V, ID =

- 0.20 A

.. Forward Transconductance a

Diode Forward Voltage a gfs VSD

VDS =

- 10 V, ID =

- 0.53 A IS =

- 0.23 A, VGS = 0 V

Dynamic b

Total Gate Charge Gate-Source Charge Gate-Drain Charge Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Source-Drain Reverse Recovery Time

Qg Qgs Qgd td(on) tr td(off) tf trr IF...