EDI88128CS

EDI88128CS is 128Kx8 Monolithic SRAM manufactured by White Electronic Designs.

White Electronic Designs

128Kx8 Monolithic SRAM, SMD 5962-89598

Features

- Access Times of 15- , 17, 20, 25, 35, 45, 55ns

- CS# and OE# Functions for Bus Control

- 2V Data Retention (EDI88128LPS)

- TTL patible Inputs and Outputs

- Fully Static, No Clocks

- 32 pad Ceramic LCC (Package 141)

- 32 lead Ceramic Flatpack (Package 142)

- Single +5V (±10%) Supply OperationThe EDI88128CS is a high speed, high performance, 128Kx8 megabit density Monolithic CMOS Static RAM.

- Organized as 128Kx8

- mercial, Industrial and Military Temperature

Ranges

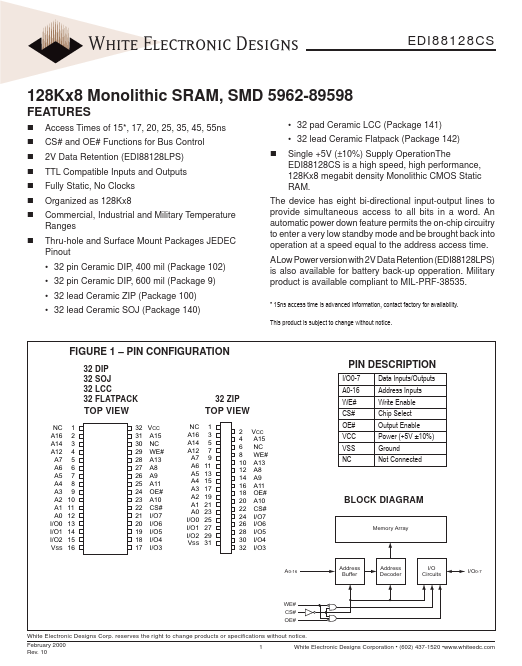

- Thru-hole and Surface Mount Packages JEDEC

Pinout

- 32 pin Ceramic DIP, 400 mil (Package 102)

- 32 pin Ceramic DIP, 600 mil...