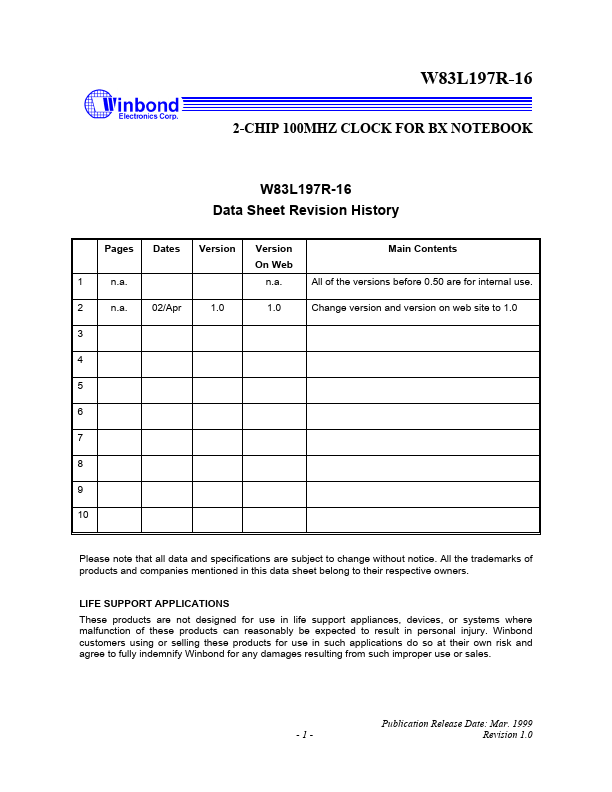

W83L197R-16

W83L197R-16 is 2-CHIP 100MHZ CLOCK FOR BX NOTEBOOK manufactured by Winbond.

DESCRIPTION

The W83L197R-16 is a Clock Synthesizer which provides all clocks required for high-speed RISC or CISC microprocessor. Four different frequency of CPU, and PCI clocks are externally selectable with smooth transitions. The 0.5% or 0.75% center type spread spectrum can be selected to reduce EMI. The W83L197R-16 accepts a 14.318 MHz reference crystal as its input and runs on a 3.3V supply. High drive PCI CLOCK outputs typically provide greater than 1 V /ns slew rate into 30 p F loads. CPU CLOCK outputs typically provide better than 1 V /ns slew rate into 20 p F loads as maintaining 50± 5% duty cycle. The fixed frequency outputs as REF, 48 MHz provide better than 0.5V /ns slew rate.

2.0 PRODUCT FEATURES

- -

- -

- -

- -

- - Supports Pentium II CPUs 4 sets of CPU frequencies selection 2 CPU clocks (one free running CPU clock) 6 PCI synchronous clocks(one free running PCI clock) Optional single or mixed supply: (Vdd3 = Vdd C= 3.3V±5%) or (Vdd C = 2.5V±5%) Skew form CPU to PCI clock 1.5 to 4.0 ns, CPU leads. CPU clock jitter less than 200ps PCI_F,PCI1:6 clock skew less than 500ps ±0.5% or ±0.75% center type spread spectrum function to reduce EMI Programmable registers to enable/stop each output and select modes (mode as Tri-state or Normal )

- 48 MHz for USB

- 28-pin SOP package (209mil)

3.0 BLOCK DIAGRAM

Publication Release Date: Mar. 1999 Revision 1.0

-2-

X1 X2 CPU_STOP# SEL100/66#

XTAL OSC

Vdd3 REF2X

Spread Spectrum ÷2/3/4

PLL1

Vdd C

STOP

CPUCLK0 CPUCLK1

Vdd3 PCI clock Divder PCI_STOP# PWR_DWN# Power down control PCICLK_F

STOP

Vdd3 5

PCICLK(1:5)

Vdd3 48MHz

PLL2

4.0 PIN CONFIGURATION

Xin Xout Vss PCICLK_F PCICLK1 Vdd3 PCICLK2 PCICLK3 Vdd3 PCICLK4 PCICLK5 Vss Vdd3 Vss 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Vss Vdd3 REF2X/FS0- Vdd C CPUCLK0 CPUCLK1 Vss Vdd3 Vss PCI_STOP# CPU_STOP# PWR_DWN# 48MHz/SPREAD- SEL100/66#

5.0 PIN DESCRIPTION

- Input Publication Release Date: Mar. 1999 Revision...