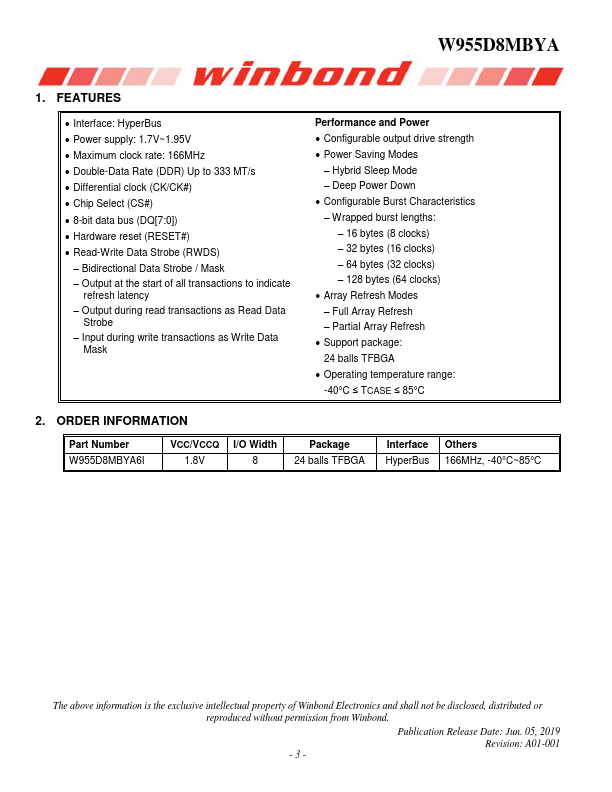

W955D8MBYA

FEATURES

- Interface: Hyper Bus

- Power supply: 1.7V~1.95V

- Maximum clock rate: 166MHz

- Double-Data Rate (DDR) Up to 333 MT/s

- Differential clock (CK/CK#)

- Chip Select (CS#)

- 8-bit data bus (DQ[7:0])

- Hardware reset (RESET#)

- Read-Write Data Strobe (RWDS)

- Bidirectional Data Strobe / Mask

- Output at the start of all transactions to indicate refresh latency

- Output during read transactions as Read Data

Strobe

- Input during write transactions as Write Data

Mask

Performance and Power

- Configurable output drive strength

- Power Saving Modes

- Hybrid Sleep Mode

- Deep Power Down

- Configurable Burst Characteristics

- Wrapped burst lengths:

- 16 bytes (8 clocks)

- 32 bytes (16 clocks)

- 64 bytes (32 clocks)

- 128 bytes (64 clocks)

- Array Refresh Modes

- Full Array Refresh

- Partial Array Refresh

- Support package: 24 balls TFBGA

- Operating temperature range: -40°C ≤ TCASE ≤ 85°C

2. ORDER INFORMATION

Part Number W955D8MBYA6I

VCC/VCCQ I/O Width

1.8V

Package 24 balls...