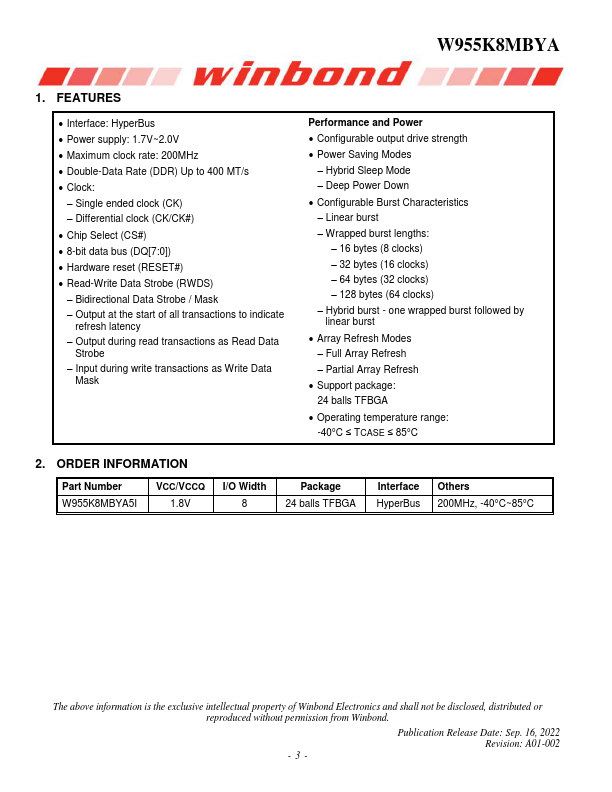

| Part | W955K8MBYA |

|---|---|

| Description | 32Mb HyperRAM |

| Manufacturer | Winbond |

| Size | 689.07 KB |

Pricing from 5.08202 USD, available from DigiKey and Arrow Electronics.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| DigiKey | 0 | 480+ : 5.08202 USD | View Offer |

| Arrow Electronics | 0 | 480+ : 3.746 USD 500+ : 3.708 USD 1000+ : 3.671 USD 2000+ : 3.635 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| S27KL0642 | Cypress | HyperRAM Self-Refresh DRAM |

| IS67WVH8M8BLL | ISSI | 8M x 8 HyperRAM |

| W956A8MBYA | Winbond | 64Mb HyperRAM |