17S50A

17S50A is Spartan-II/Spartan-IIE Family OTP Configuration PROMs manufactured by Xilinx.

- Part of the 17S15APC comparator family.

- Part of the 17S15APC comparator family.

Features

Configuration one-time programmable (OTP) read-only memory designed to store configuration bitstreams for Spartan-II/Spartan-IIE FPGA devices

- Simple interface to the Spartan device

- Programmable reset polarity (active High or active Low)

- Low-power CMOS floating gate process ..

- 3.3V PROM

- -

- -

- Available in pact plastic 8-pin DIP, 8-pin VOIC, 20-pin SOIC, or 44-pin VQFP packages. Programming support by leading programmer manufacturers. Design support using the Xilinx Alliance and Foundation series software packages. Guaranteed 20-year life data retention

Introduction

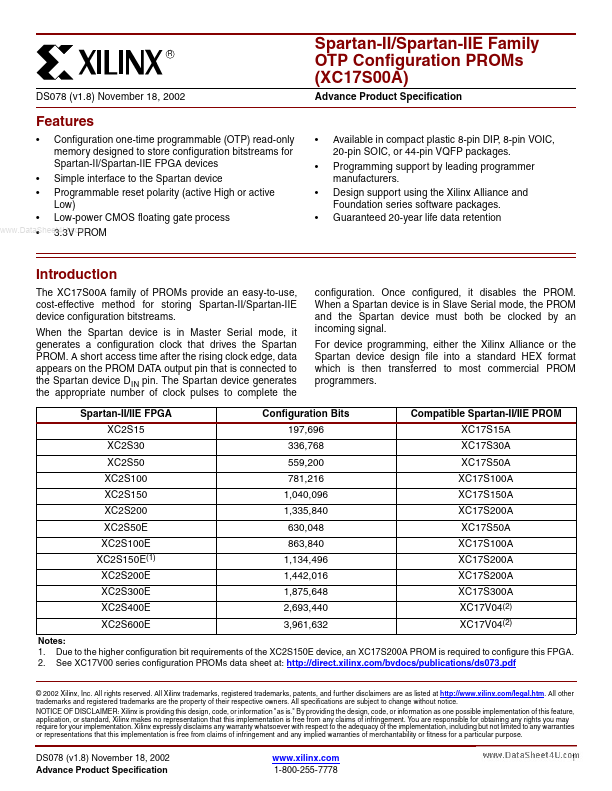

The XC17S00A family of PROMs provide an easy-to-use, cost-effective method for storing Spartan-II/Spartan-IIE device configuration bitstreams. When the Spartan device is in Master Serial mode, it generates a configuration clock that drives the Spartan PROM. A short access time after the rising clock edge, data appears on the PROM DATA output pin that is connected to the Spartan device D IN pin. The Spartan device generates the appropriate number of clock pulses to plete the Spartan-II/IIE FPGA XC2S15 XC2S30 XC2S50 XC2S100 XC2S150 XC2S200 XC2S50E XC2S100E XC2S150E(1) XC2S200E XC2S300E XC2S400E XC2S600E configuration. Once configured, it disables the PROM. When a Spartan device is in Slave Serial mode, the PROM and the Spartan device must both be clocked by an ining signal. For device programming, either the Xilinx Alliance or the Spartan device design file into a standard HEX format which is then transferred to most mercial PROM programmers. patible Spartan-II/IIE PROM XC17S15A XC17S30A XC17S50A XC17S100A XC17S150A XC17S200A XC17S50A XC17S100A XC17S200A XC17S200A XC17S300A XC17V04(2) XC17V04(2)

Configuration Bits 197,696 336,768 559,200 781,216 1,040,096 1,335,840 630,048 863,840 1,134,496 1,442,016 1,875,648 2,693,440 3,961,632

Notes: 1. Due to the higher configuration bit requirements of the XC2S150E device, an XC17S200A PROM is required to configure this FPGA. 2. See XC17V00...