Datasheet Summary

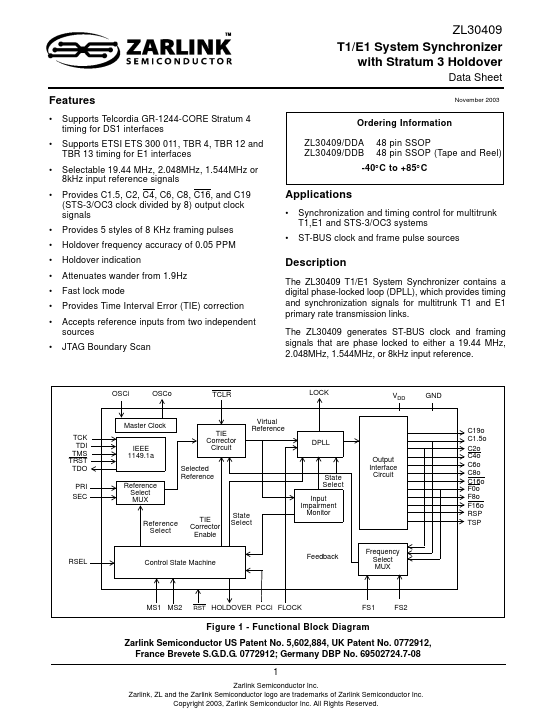

ZL30409 T1/E1 System Synchronizer with Stratum 3 Holdover

Data Sheet Features

- -

- - Supports Telcordia GR-1244-CORE Stratum 4 timing for DS1 interfaces Supports ETSI ETS 300 011, TBR 4, TBR 12 and TBR 13 timing for E1 interfaces Selectable 19.44 MHz, 2.048MHz, 1.544MHz or 8kHz input reference signals Provides C1.5, C2, C4, C6, C8, C16, and C19 (STS-3/OC3 clock divided by 8) output clock signals Provides 5 styles of 8 KHz framing pulses Holdover frequency accuracy of 0.05 PPM Holdover indication Attenuates wander from 1.9Hz Fast lock mode Provides Time Interval Error (TIE) correction Accepts reference inputs from two independent sources JTAG Boundary Scan

- Ordering Information...