MT8941B

MT8941B is Advanced T1/CEPT Digital Trunk PLL manufactured by Zarlink Semiconductor.

MT8941B Advanced T1/CEPT Digital Trunk PLL

Data Sheet Features

- - Provides T1 clock at 1.544 MHz locked to an 8 k Hz reference clock (frame pulse) Provides CEPT clock at 2.048 MHz and ST-BUS clock and timing signals locked to an internal or external 8 k Hz reference clock Typical inherent output jitter (unfiltered)= 0.07 UI peak-to-peak Typical jitter attenuation at: 10 Hz=23 d B,100 Hz=43 d B, 5 to 40 k Hz ≥ 64 d B Jitter-free “FREE-RUN” mode Unmitted two-input NAND gate Low power CMOS technology Ordering Information

MT8941BE 24 Pin PDIP Tubes MT8941BP 28 Pin PLCC Tubes MT8941BPR 28 Pin PLCC Tape & Reel MT8941BP1 28 Pin PLCC- Tubes MT8941BPR1 28 Pin PLCC- Tape & Reel

- Pb Free Matte Tin

February 2005

- -

- -

- -40° C to +85 ° C

Description

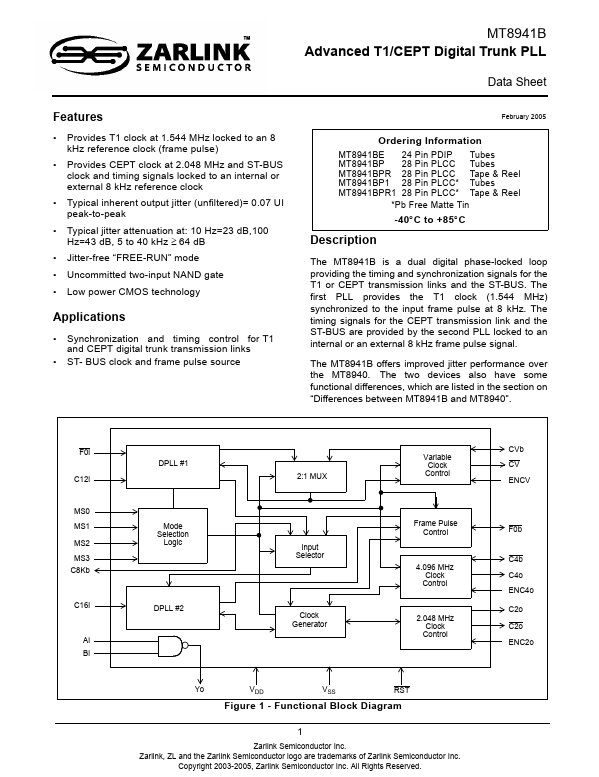

The MT8941B is a dual digital phase-locked loop providing the timing and synchronization signals for the T1 or CEPT transmission links and the ST-BUS. The first PLL provides the T1 clock (1.544 MHz) synchronized to the input frame pulse at 8 k Hz. The timing signals for the CEPT transmission link and the ST-BUS are provided by the second PLL locked to an internal or an external 8 k Hz frame pulse signal. The MT8941B offers improved jitter performance over the MT8940. The two devices also have some functional differences, which are listed in the section on “Differences between MT8941B and MT8940”.

Applications

- - Synchronization and timing control for T1 and CEPT digital trunk transmission links ST- BUS clock and frame pulse source

F0i DPLL #1 C12i 2:1 MUX

Variable Clock Control

CVb CV ENCV

MS0 MS1 MS2 MS3 C8Kb Mode Selection Logic Frame Pulse Control Input Selector 4.096 MHz Clock Control DPLL #2 F0b

C4b C4o ENC4o C2o C2o ENC2o

C16i

Clock Generator

Ai Bi

2.048 MHz Clock Control

Yo

Figure 1

- Functional Block Diagram 1

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2003-2005, Zarlink Semiconductor Inc. All Rights...