| Part | PDSP16116A |

|---|---|

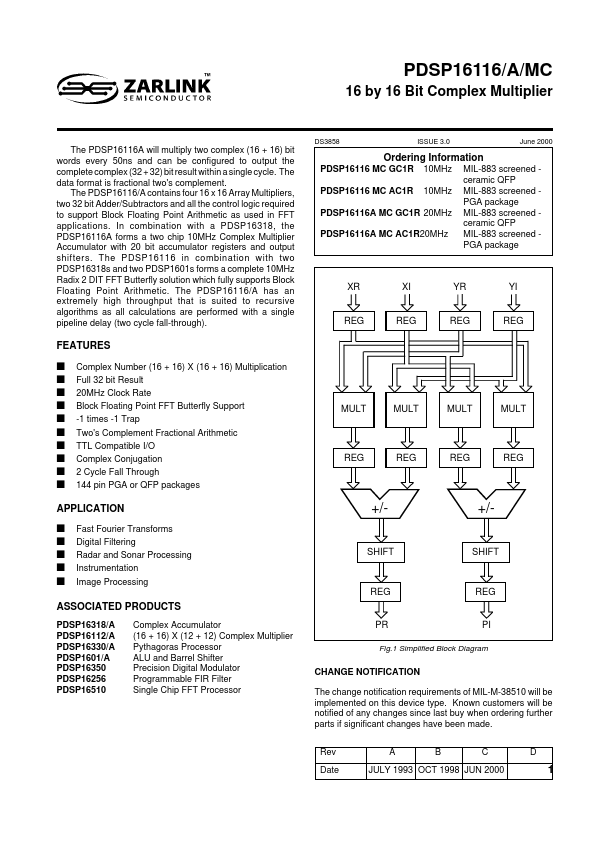

| Description | 16 by 16 Bit Complex Multiplier |

| Manufacturer | Zarlink Semiconductor |

| Size | 174.85 KB |

Related Datasheets

- PDSP16116AMCGGDR — Mitel Networks Corporation — 16 X 16 Bit Complex Multiplier

- PDSP16116 — Mitel Networks Corporation — 16 X 16 Bit Complex Multiplier

- PDSP16116MCGGDR — Mitel Networks Corporation — 16 X 16 Bit Complex Multiplier