ZL50410

Key Features

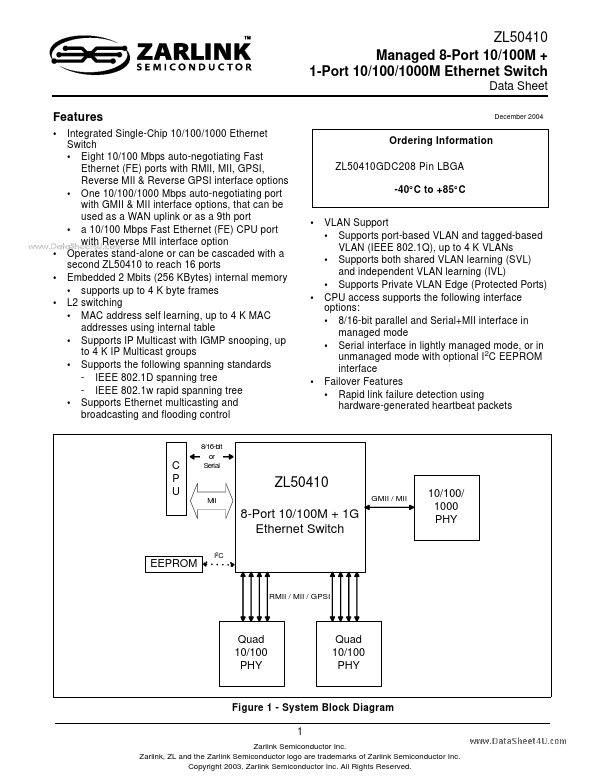

- Integrated Single-Chip 10/100/1000 Ethernet Switch

- Eight 10/100 Mbps auto-negotiating Fast Ethernet (FE) ports with RMII, MII, GPSI, Reverse MII & Reverse GPSI interface options

- One 10/100/1000 Mbps auto-negotiating port with GMII & MII interface options, that can be used as a WAN uplink or as a 9th port

- a 10/100 Mbps Fast Ethernet (FE) CPU port with Reverse MII interface option

- Operates stand-alone or can be cascaded with a second ZL50410 to reach 16 ports