ZL30106

ZL30106 is SONET/SDH/PDH Network Interface DPLL manufactured by Zarlink.

Features

- Synchronizes to clock-and-sync-pair to maintain minimal phase skew between inputs and outputs

- Supports output wander and jitter generation specifications for SONET/SDH and PDH interfaces

- Accepts three input references and synchronizes to any bination of 2 k Hz, 8 k Hz, 1.544 MHz, 2.048 MHz, 8.192 MHz, 16.384 MHz or 19.44 MHz inputs

- Provides a range of clock outputs:

- 2.048 MHz (E1), 16.384 MHz and either 4.096 MHz and 8.192 MHz or 32.768 MHz and 65.536 MHz

- 19.44 MHz (SONET/SDH)

- 1.544 MHz (DS1) and 3.088 MHz

- a choice of 6.312 MHz (DS2), 8.448 MHz (E2), 44.736 MHz (DS3) or 34.368 MHz (E3)

- Provides 5 styles of 8 k Hz framing pulses and a 2 k Hz multi-frame pulse

- Provides automatic entry into Holdover and return from Holdover

- Manual and automatic hitless reference switching between any bination of valid input reference frequencies

April 2010

Ordering Information

ZL30106QDG1 64 pin TQFP- Trays, Bake & Drypack

- Pb Free Matte Tin -40°C to +85°C

- Provides lock, holdover and accurate reference fail indication

- Selectable loop filter bandwidth of 29 Hz or 922 Hz

- Less than 24 psrms intrinsic jitter on the 19.44 MHz output clock, pliant with GR-253CORE OC-3 and G.813 STM-1 specifications

- Less than 0.6 nspp intrinsic jitter on all PDH output clocks and frame pulses

- Selectable external master clock source: clock oscillator or crystal

- Simple hardware control interface

Applications

- Line card synchronization for SONET/SDH and PDH systems

- Wireless base-station Network Interface Card

- Advanced TCA™ and H.110 line cards

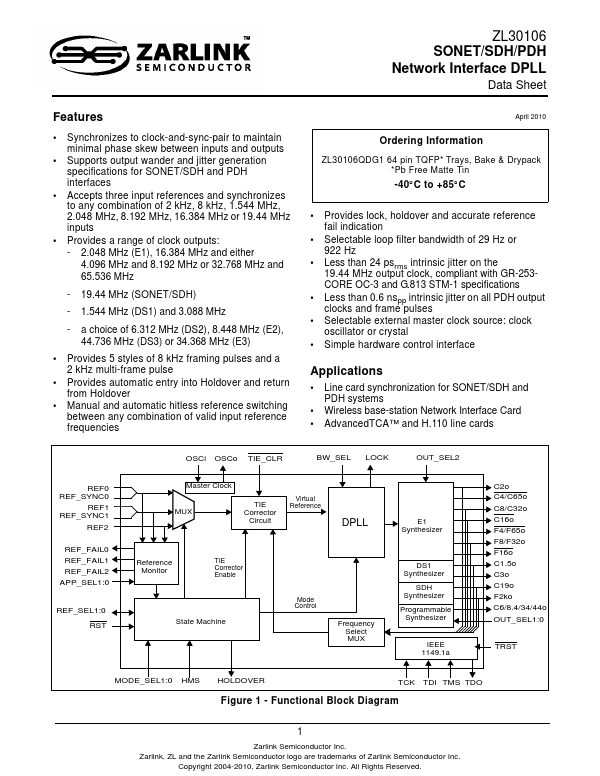

OSCi OSCo TIE_CLR

BW_SEL LOCK

OUT_SEL2

REF0 REF_SYNC0

REF1 REF_SYNC1

REF2

REF_FAIL0 REF_FAIL1 REF_FAIL2 APP_SEL1:0

REF_SEL1:0 RST

Master Clock MUX

TIE Corrector

Circuit

Virtual Reference

DPLL

E1...