ZL30108

Overview

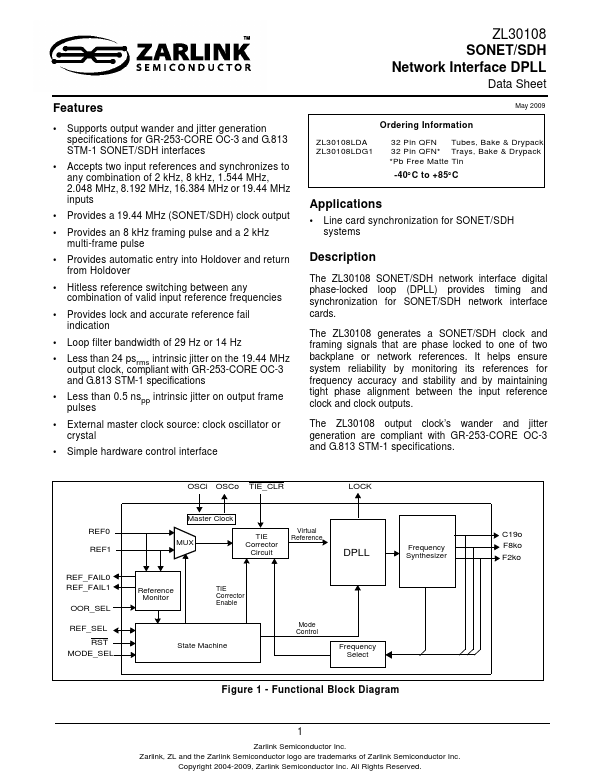

The ZL30108 SONET/SDH network interface digital phase-locked loop (DPLL) provides timing and synchronization for SONET/SDH network interface cards. The ZL30108 generates a SONET/SDH clock and framing signals that are phase locked to one of two backplane or network references.

- Supports output wander and jitter generation specifications for GR-253-CORE OC-3 and G.813 STM-1 SONET/SDH interfaces

- Accepts two input references and synchronizes to any combination of 2 kHz, 8 kHz, 1.544 MHz, 2.048 MHz, 8.192 MHz, 16.384 MHz or 19.44 MHz inputs

- Provides a 19.44 MHz (SONET/SDH) clock output

- Provides an 8 kHz framing pulse and a 2 kHz multi-frame pulse

- Provides automatic entry into Holdover and return from Holdover

- Hitless reference switching between any combination of valid input reference frequencies

- Provides lock and accurate reference fail indication

- Loop filter bandwidth of 29 Hz or 14 Hz

- Less than 24 psrms intrinsic jitter on the 19.44 MHz output clock, compliant with GR-253-CORE OC-3 and G.813 STM-1 specifications

- Less than 0.5 nspp intrinsic jitter on output frame pulses