ZL30107

Overview

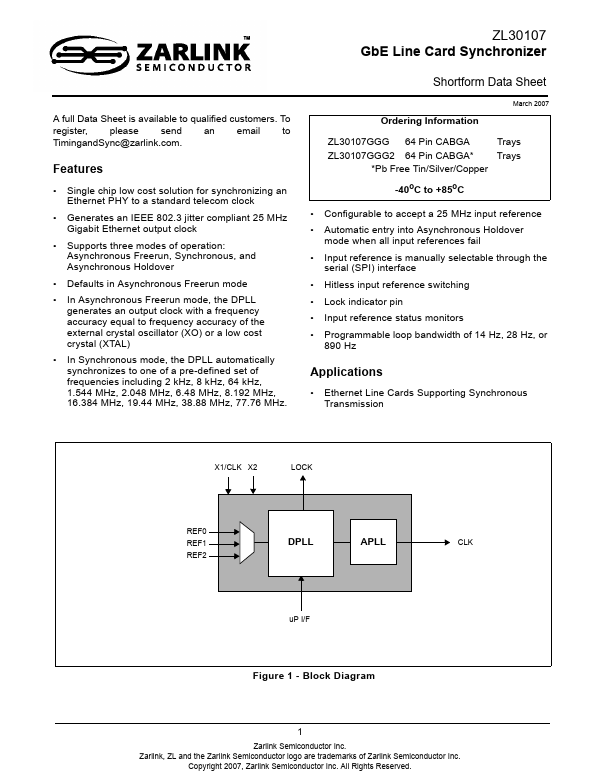

- Single chip low cost solution for synchronizing an Ethernet PHY to a standard telecom clock Generates an IEEE 802.3 jitter compliant 25 MHz Gigabit Ethernet output clock Supports three modes of operation: Asynchronous Freerun, Synchronous, and Asynchronous Holdover Defaults in Asynchronous Freerun mode In Asynchronous Freerun mode, the DPLL generates an output clock with a frequency accuracy equal to frequency accuracy of the external crystal oscillator (XO) or a low cost crystal (XTAL) In Synchronous mode, the DPLL automatically synchronizes to one of a pre-defined set of frequencies including 2 kHz, 8 kHz, 64 kHz, 1.544 MHz, 2.048 MHz, 6.48 MHz, 8.192 MHz, 16.384 MHz, 19.44 MHz, 38.88 MHz, 77.76 MHz. * *