FRAME-IT-1 Overview

Key Features

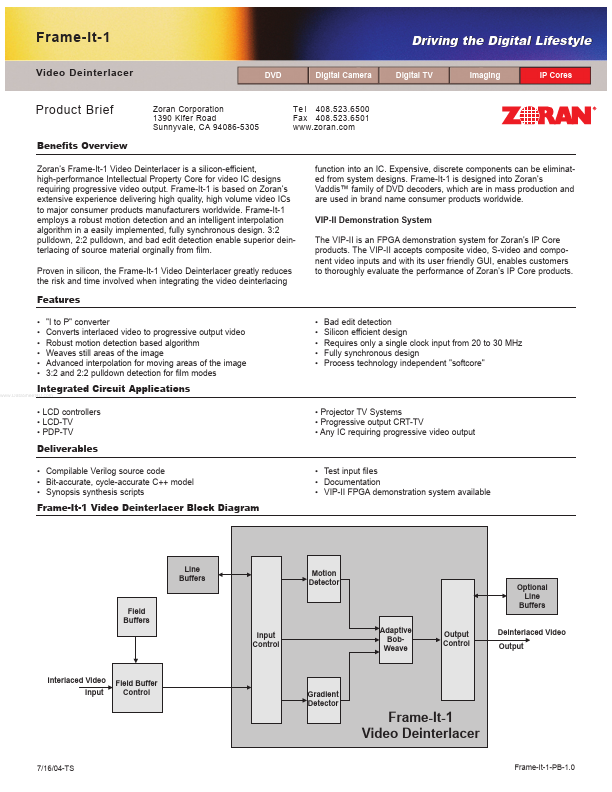

- "I to P" converter Converts interlaced video to progressive output video Robust motion detection based algorithm Weaves still areas of the image Advanced interpolation for moving areas of the image 3:2 and 2:2 pulldown detection for film modes

- Bad edit detection Silicon efficient design Requires only a single clock input from 20 to 30 MHz Fully synchronous design Process technology independent "softcore"