54ACT11821

54ACT11821 is 10-BIT BUS-INTERFACE FLIP-FLOPS manufactured by Texas Instruments.

- Inputs Are TTL-Voltage patible

- Provides Extra Data Width Necessary for

Wider Address/Data Paths or Buses With

Parity

- Flow-Through Architecture Optimizes

PCB Layout

- Center-Pin VCC and GND Configurations

Minimize High-Speed Switching Noise

- EPIC™ (Enhanced-Performance Implanted

CMOS) 1-µm Process

- 500-m A Typical Latch-Up Immunity at 125°C

- Package Options Include Plastic

Small-Outline Packages, Ceramic Chip

Carriers, and Standard Ceramic 300-mil

DIPs description

54ACT11821, 74ACT11821 10-BIT BUS-INTERFACE FLIP-FLOPS

WITH 3-STATE OUTPUTS

SCAS156A

- NOVEMBER 1990

- REVISED APRIL 1993

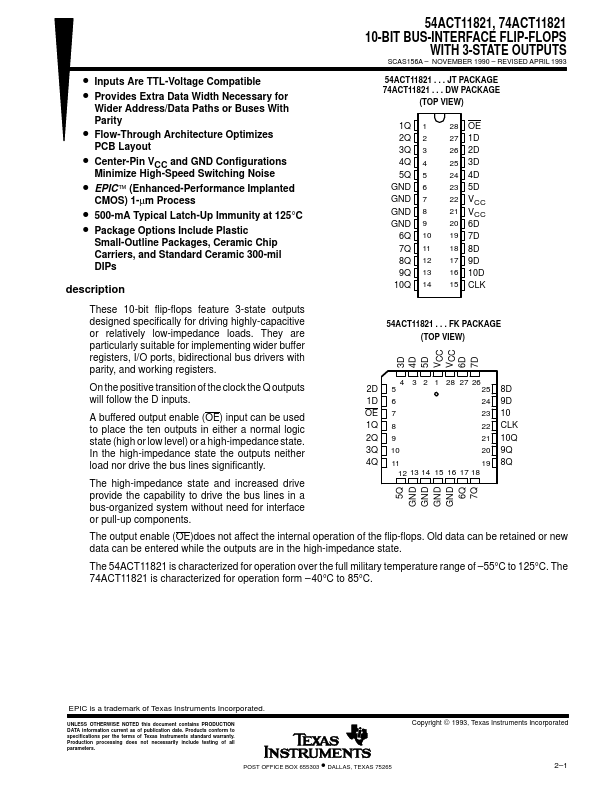

54ACT11821 . . . JT PACKAGE 74ACT11821 . . . DW PACKAGE

(TOP VIEW)

1Q 2Q 3Q 4Q 5Q GND GND GND GND 6Q 7Q 8Q 9Q 10Q

1 2 3 4 5 6 7 8 9 10 11 12 13 14

28 OE 27 1D 26 2D 25 3D 24 4D 23 5D 22 VCC 21 VCC 20 6D 19 7D 18 8D 17 9D 16 10D 15 CLK

These 10-bit flip-flops feature 3-state outputs designed specifically for driving highly-capacitive or relatively low-impedance loads. They are particularly suitable for implementing wider buffer registers, I/O ports, bidirectional bus drivers with parity, and working registers.

On the positive transition of the clock the Q outputs will follow the D inputs.

A buffered output enable (OE) input can be used to place the ten outputs in either a normal logic state (high or low level) or a high-impedance state. In the high-impedance state the outputs neither load nor drive the bus lines significantly.

The high-impedance state and increased drive provide the capability to drive the bus lines in a bus-organized system without need for interface or pull-up ponents.

5Q GND GND GND...