54ACT175

54ACT175 is Quad D Flip-Flop manufactured by Texas Instruments.

- Part of the 54AC175 comparator family.

- Part of the 54AC175 comparator family.

FEATURES

- 2 Edge-Triggered D-Type Inputs

- Buffered Positive Edge-Triggered Clock

- Asynchronous mon Reset

- True and plement Output

- Outputs Source/Sink 24 m A

- 'ACT175 has TTL-patible Inputs

- Standard Microcircuit Drawing (SMD)

- 'AC175: 5962-89552

- 'ACT175: 5962-89693

DESCRIPTION

The 'AC/'ACT175 is a high-speed quad D flip-flop. The device is useful for general flip-flop requirements where clock and clear inputs are mon. The information on the D inputs is stored during the LOWto-HIGH clock transition. Both true and plemented outputs of each flip-flop are provided. A Master Reset input resets all flip-flops, independent of the Clock or D inputs, when LOW.

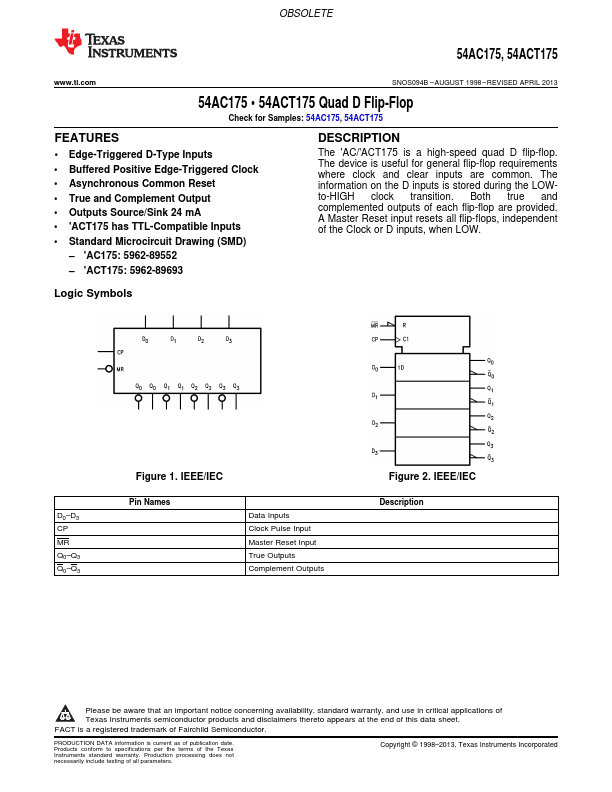

Logic Symbols

D0- D3 CP MR Q0- Q3 Q0- Q3

Figure 1. IEEE/IEC

Pin Names

Data Inputs Clock Pulse Input Master Reset Input True Outputs plement Outputs

Figure 2. IEEE/IEC

Description

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. FACT is a registered trademark of Fairchild Semiconductor.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1998- 2013, Texas Instruments Incorporated

54AC175, 54ACT175

SNOS094B

- AUGUST 1998

- REVISED APRIL 2013

Connection Diagrams

OBSOLETE

.ti.

Figure 3. Pin Assignment for CDIP and CLGA See Package Numbers NFE and NAD

Figure 4. Pin Assignment for LCCC See Package Number NAJ

Functional Description

The 'AC/'ACT175 consists of four edge-triggered D flip-flops with individual D inputs and Q and Q outputs. The Clock and Master Reset are mon. The four flip-flops will store the state of their individual D inputs on the LOW-to-HIGH clock (CP) transition, causing individual Q and Q outputs to follow. A LOW...