ADC10DV200

ADC10DV200 is Dual 10-bit 200MSPS Low-Power A/D Converter manufactured by Texas Instruments.

.ti.

SNAS471A

- FEBRUARY 2009

- REVISED APRIL 2013

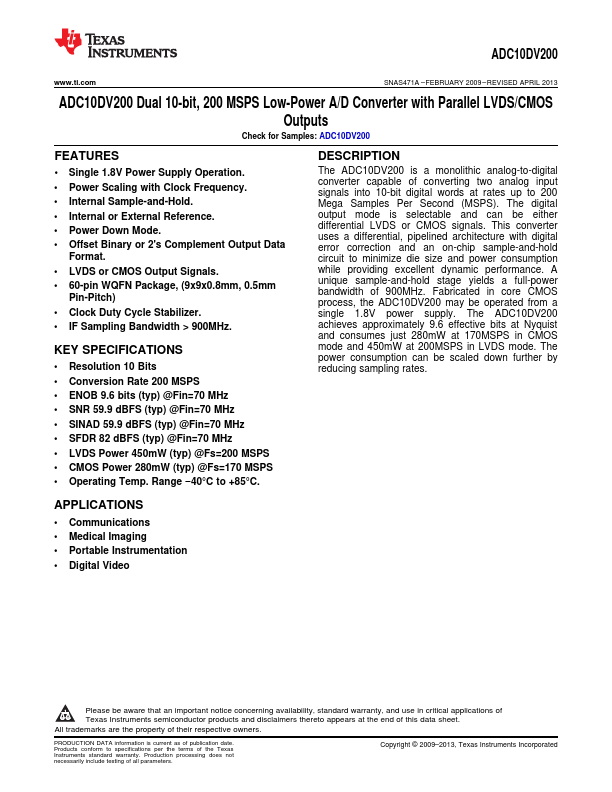

ADC10DV200 Dual 10-bit, 200 MSPS Low-Power A/D Converter with Parallel LVDS/CMOS Outputs

Check for Samples: ADC10DV200

Features

- 2 Single 1.8V Power Supply Operation.

- Power Scaling with Clock Frequency.

- Internal Sample-and-Hold.

- Internal or External Reference.

- Power Down Mode.

- Offset Binary or 2's plement Output Data

Format.

- LVDS or CMOS Output Signals.

- 60-pin WQFN Package, (9x9x0.8mm, 0.5mm

Pin-Pitch)

- Clock Duty Cycle Stabilizer.

- IF Sampling Bandwidth > 900MHz.

KEY SPECIFICATIONS

- Resolution 10 Bits

- Conversion Rate 200 MSPS

- ENOB 9.6 bits (typ) @Fin=70 MHz

- SNR 59.9 d BFS (typ) @Fin=70 MHz

- SINAD 59.9 d BFS (typ) @Fin=70 MHz

- SFDR 82 d BFS (typ) @Fin=70 MHz

- LVDS Power 450m W (typ) @Fs=200 MSPS

- CMOS Power 280m W (typ) @Fs=170 MSPS

- Operating Temp. Range

- 40°C to...