ADC128S102QML-SP

Overview

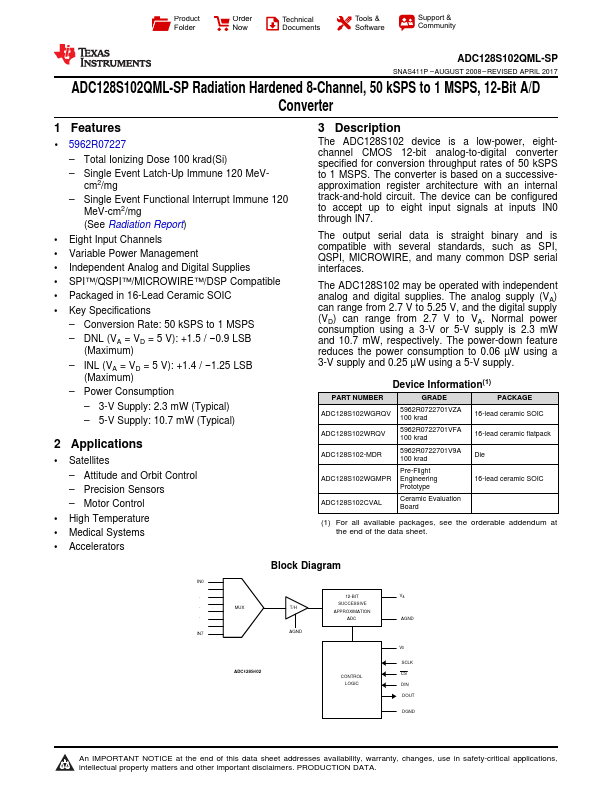

The ADC128S102 device is a low-power, eightchannel CMOS 12-bit analog-to-digital converter specified for conversion throughput rates of 50 kSPS to 1 MSPS. The converter is based on a successiveapproximation register architecture with an internal track-and-hold circuit.

- 1 5962R07227 - Total Ionizing Dose 100 krad(Si) - Single Event Latch-Up Immune 120 MeVcm2/mg - Single Event Functional Interrupt Immune 120 MeV-cm2/mg (See Radiation Report)

- Eight Input Channels

- Variable Power Management

- Independent Analog and Digital Supplies

- SPI™/QSPI™/MICROWIRE™/DSP Compatible

- Packaged in 16-Lead Ceramic SOIC

- Key Specifications - Conversion Rate: 50 kSPS to 1 MSPS - DNL (VA = VD = 5 V): +1.5 / -0.9 LSB (Maximum) - INL (VA = VD = 5 V): +1.4 / -1.25 LSB (Maximum) - Power Consumption - 3-V Supply: 2.3 mW (Typical) - 5-V Supply: 10.7 mW (Typical)