Datasheet Summary

ADC3568, ADC3569

SBASAO4A

- DECEMBER 2024

- REVISED JANUARY 2025

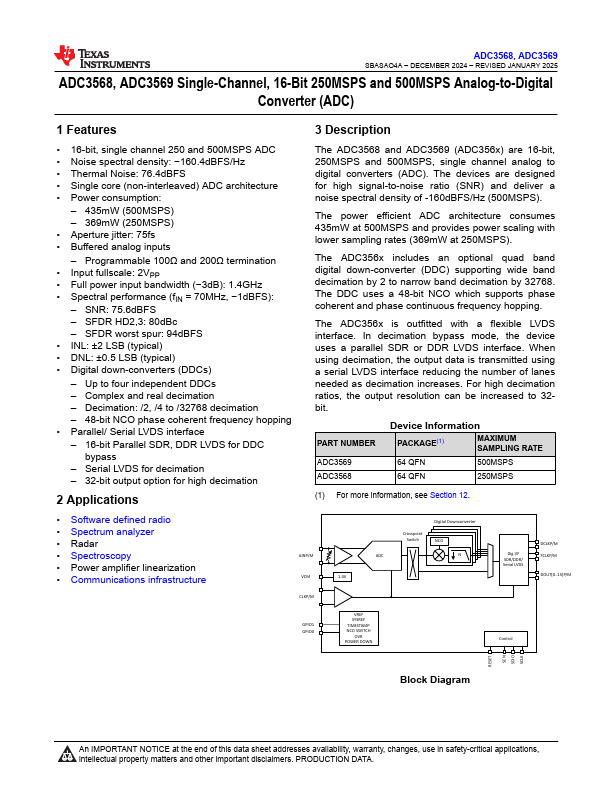

ADC3568, ADC3569 Single-Channel, 16-Bit 250MSPS and 500MSPS Analog-to-Digital Converter (ADC)

1 Features

3 Description

- 16-bit, single channel 250 and 500MSPS ADC

- Noise spectral density:

- 160.4dBFS/Hz

- Thermal Noise: 76.4dBFS

- Single core (non-interleaved) ADC architecture

- Power consumption:

- 435mW (500MSPS)

- 369mW (250MSPS)

- Aperture jitter: 75fs

- Buffered analog inputs

- Programmable 100Ω and 200Ω termination

- Input fullscale: 2VPP

- Full power input bandwidth (- 3dB): 1.4GHz

- Spectral performance (fIN = 70MHz,

- 1dBFS):

- SNR: 75.6dBFS

- SFDR HD2,3: 80dBc

- SFDR worst spur: 94dBFS

- INL: ±2 LSB (typical)

-...