ADS58J89

ADS58J89 is Quad Channel 14-Bit 250/500 MSPS Receiver and Feedback manufactured by Texas Instruments.

Product Folder

Sample & Buy

Technical Documents

Tools & Software

Support & munity

SBAS659

- NOVEMBER 2014

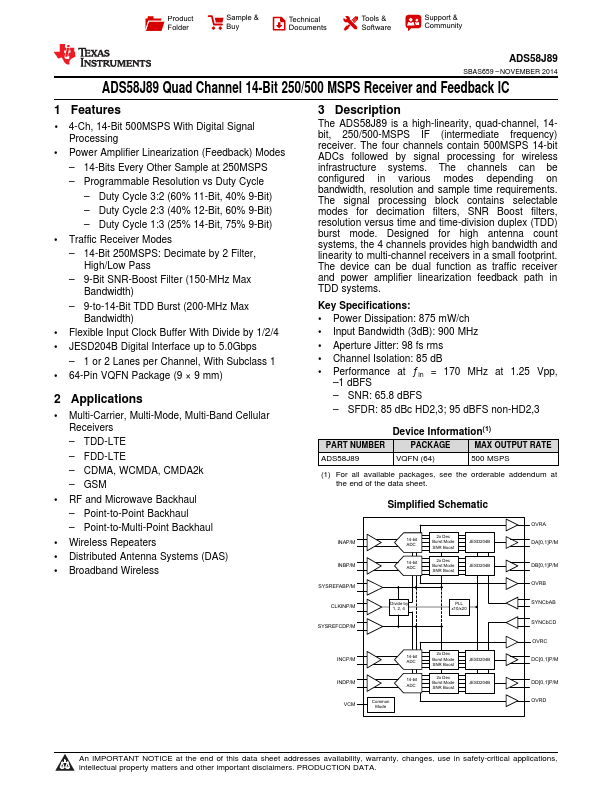

ADS58J89 Quad Channel 14-Bit 250/500 MSPS Receiver and Feedback IC

1 Features

- 1 4-Ch, 14-Bit 500MSPS With Digital Signal Processing

- Power Amplifier Linearization (Feedback) Modes

- 14-Bits Every Other Sample at 250MSPS

- Programmable Resolution vs Duty Cycle

- Duty Cycle 3:2 (60% 11-Bit, 40% 9-Bit)

- Duty Cycle 2:3 (40% 12-Bit, 60% 9-Bit)

- Duty Cycle 1:3 (25% 14-Bit, 75% 9-Bit)

- Traffic Receiver Modes

- 14-Bit 250MSPS: Decimate by 2 Filter, High/Low Pass

- 9-Bit SNR-Boost Filter (150-MHz Max Bandwidth)

- 9-to-14-Bit TDD Burst (200-MHz Max Bandwidth)

- Flexible...