ADS6122

Overview

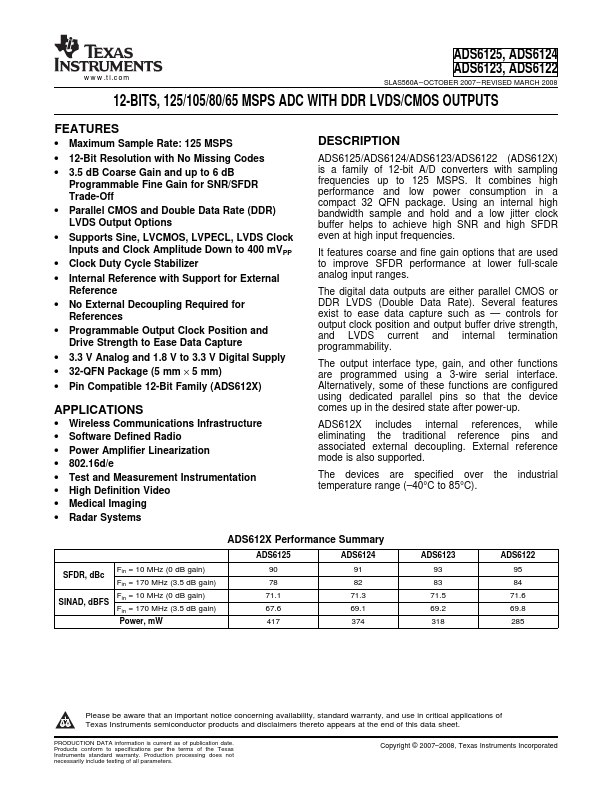

ADS6125/ADS6124/ADS6123/ADS6122 (ADS612X) is a family of 12-bit A/D converters with sampling frequencies up to 125 MSPS. It combines high performance and low power consumption in a compact 32 QFN package.

- Maximum Sample Rate: 125 MSPS

- 12-Bit Resolution with No Missing Codes

- 3.5 dB Coarse Gain and up to 6 dB Programmable Fine Gain for SNR/SFDR Trade-Off

- Parallel CMOS and Double Data Rate (DDR) LVDS Output Options

- Supports Sine, LVCMOS, LVPECL, LVDS Clock Inputs and Clock Amplitude Down to 400 mVPP

- Clock Duty Cycle Stabilizer

- Internal Reference with Support for External Reference

- No External Decoupling Required for References

- Programmable Output Clock Position and Drive Strength to Ease Data Capture

- 3.3 V Analog and 1.8 V to 3.3 V Digital Supply