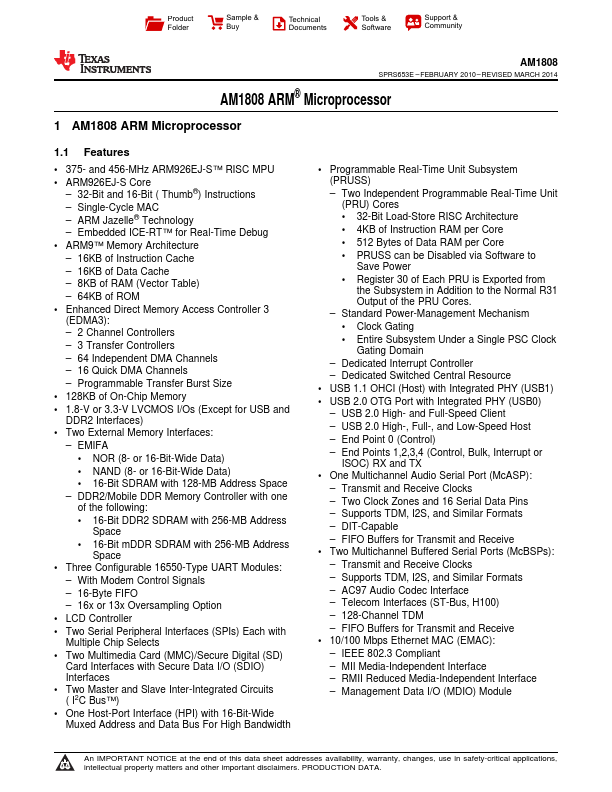

AM1808

Overview

- 375- and 456-MHz ARM926EJ-S™ RISC MPU

- ARM926EJ-S Core - 32-Bit and 16-Bit ( Thumb®) Instructions - Single-Cycle MAC - ARM Jazelle® Technology - Embedded ICE-RT™ for Real-Time Debug

- ARM9™ Memory Architecture - 16KB of Instruction Cache - 16KB of Data Cache - 8KB of RAM (Vector Table) - 64KB of ROM

- Enhanced Direct Memory Access Controller 3 (EDMA3): - 2 Channel Controllers - 3 Transfer Controllers - 64 Independent DMA Channels - 16 Quick DMA Channels - Programmable Transfer Burst Size

- 128KB of On-Chip Memory

- 1.8-V or 3.3-V LVCMOS I/Os (Except for USB and DDR2 Interfaces)

- Two External Memory Interfaces: - EMIFA

- NOR (8- or 16-Bit-Wide Data)

- NAND (8- or 16-Bit-Wide Data)

- 16-Bit SDRAM with 128-MB Address Space - DDR2/Mobile DDR Memory Controller with one of the following: