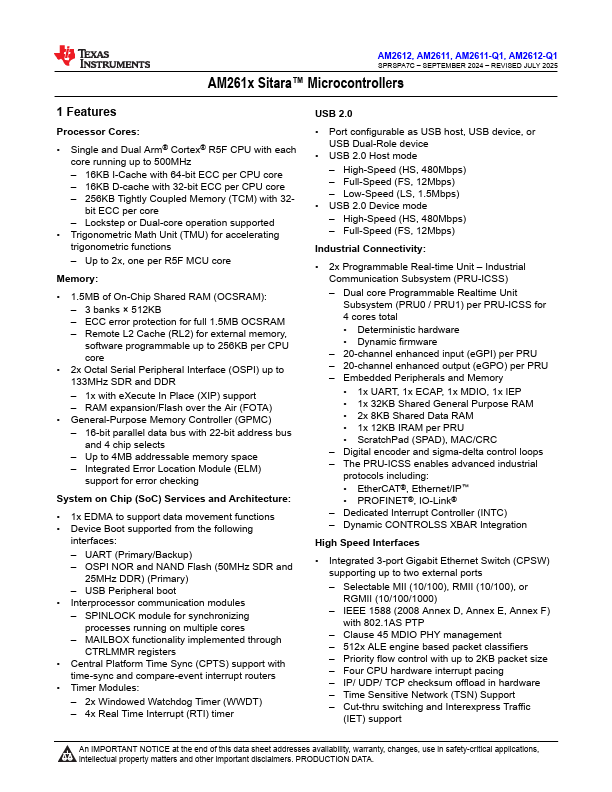

AM2612

Features

Processor Cores:

- Single and Dual Arm® Cortex® R5F CPU with each core running up to 500MHz

- 16KB I-Cache with 64-bit ECC per CPU core

- 16KB D-cache with 32-bit ECC per CPU core

- 256KB Tightly Coupled Memory (TCM) with 32bit ECC per core

- Lockstep or Dual-core operation supported

- Trigonometric Math Unit (TMU) for accelerating trigonometric functions

- Up to 2x, one per R5F MCU core

Memory:

- 1.5MB of On-Chip Shared RAM (OCSRAM):

- 3 banks × 512KB

- ECC error protection for full 1.5MB OCSRAM

- Remote L2 Cache (RL2) for external memory, software programmable up to 256KB per CPU core

- 2x Octal Serial Peripheral Interface (OSPI) up to 133MHz SDR and DDR

- 1x with e Xecute In Place (XIP) support

- RAM expansion/Flash over the Air (FOTA)

- General-Purpose Memory Controller (GPMC)

- 16-bit parallel data bus with 22-bit address bus and 4 chip selects

- Up to 4MB addressable memory space

- Integrated Error Location Module (ELM) support for error checking

System on Chip (So C)...