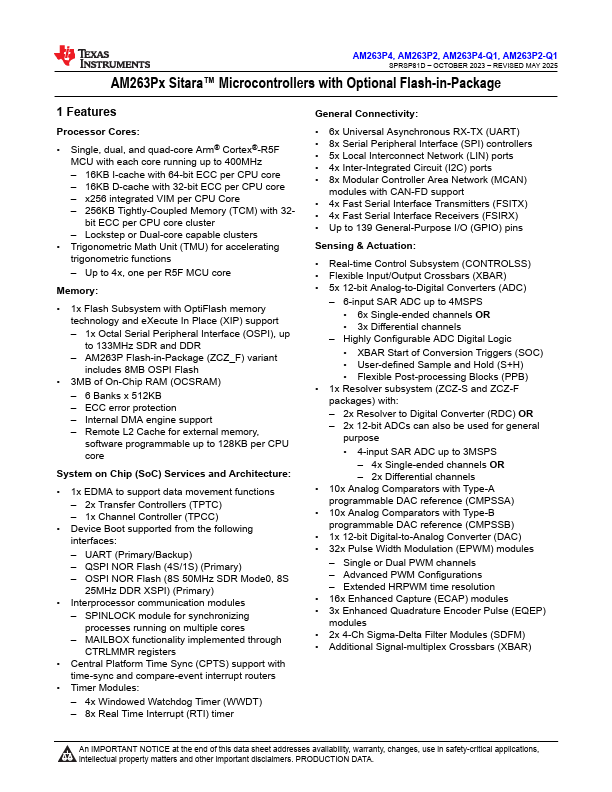

AM263P4

Overview

- Single, dual, and quad-core Arm® Cortex®-R5F MCU with each core running up to 400MHz - 16KB I-cache with 64-bit ECC per CPU core - 16KB D-cache with 32-bit ECC per CPU core - x256 integrated VIM per CPU Core - 256KB Tightly-Coupled Memory (TCM) with 32bit ECC per CPU core cluster - Lockstep or Dual-core capable clusters

- Trigonometric Math Unit (TMU) for accelerating trigonometric functions - Up to 4x, one per R5F MCU core Memory:

- 1x Flash Subsystem with OptiFlash memory technology and eXecute In Place (XIP) support - 1x Octal Serial Peripheral Interface (OSPI), up to 133MHz SDR and DDR - AM263P Flash-in-Package (ZCZ_F) variant includes 8MB OSPI Flash

- 3MB of On-Chip RAM (OCSRAM) - 6 Banks x 512KB - ECC error protection - Internal DMA engine support - Remote L2 Cache for external memory, software programmable up to 128KB per CPU core System on Chip (SoC) Services and Architecture:

- 1x EDMA to support data movement functions - 2x Transfer Controllers (TPTC) - 1x Channel Controller (TPCC)

- Device Boot supported from the following interfaces: - UART (Primary/Backup) - QSPI NOR Flash (4S/1S) (Primary) - OSPI NOR Flash (8S 50MHz SDR Mode0, 8S 25MHz DDR XSPI) (Primary)

- Interprocessor communication modules - SPINLOCK module for synchronizing processes running on multiple cores - MAILBOX functionality implemented through CTRLMMR registers

- Central Platform Time Sync (CPTS) support with time-sync and compare-event interrupt routers

- Timer Modules: - 4x Windowed Watchdog Timer (WWDT) - 8x Real Time Interrupt (RTI) timer General Connectivity:

- 6x Universal Asynchronous RX-TX (UART)