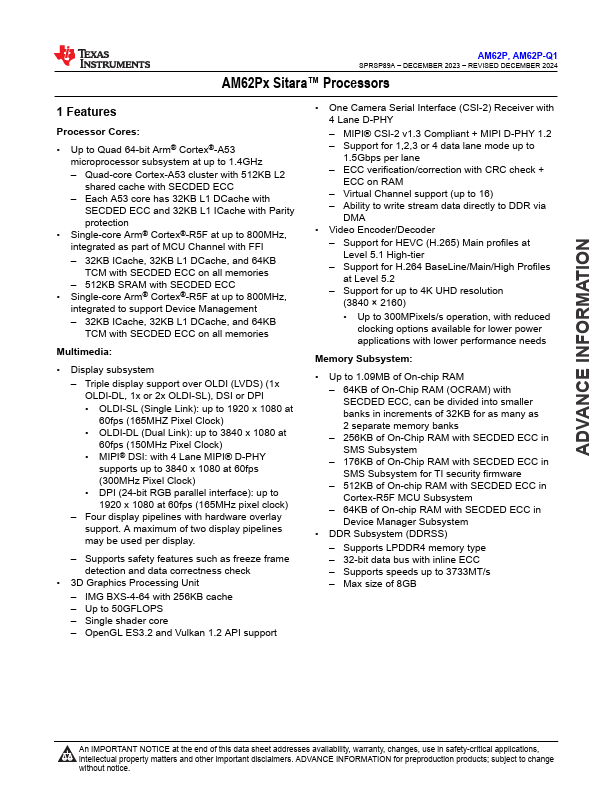

AM62P

Features

Processor Cores:

- Up to Quad 64-bit Arm® Cortex®-A53 microprocessor subsystem at up to 1.4GHz

- Quad-core Cortex-A53 cluster with 512KB L2 shared cache with SECDED ECC

- Each A53 core has 32KB L1 DCache with SECDED ECC and 32KB L1 ICache with Parity protection

- Single-core Arm® Cortex®-R5F at up to 800MHz, integrated as part of MCU Channel with FFI

- 32KB ICache, 32KB L1 DCache, and 64KB TCM with SECDED ECC on all memories

- 512KB SRAM with SECDED ECC

- Single-core Arm® Cortex®-R5F at up to 800MHz, integrated to support Device Management

- 32KB ICache, 32KB L1 DCache, and 64KB TCM with SECDED ECC on all memories

Multimedia:

- Display subsystem

- Triple display support over OLDI (LVDS) (1x OLDI-DL, 1x or 2x OLDI-SL), DSI or DPI

- OLDI-SL (Single Link): up to 1920 x 1080 at 60fps (165MHZ Pixel Clock)

- OLDI-DL (Dual Link): up to 3840 x 1080 at 60fps (150MHz Pixel Clock)

- MIPI® DSI: with 4 Lane MIPI® D-PHY supports up to 3840 x 1080 at 60fps (300MHz Pixel Clock)

- DPI (24-bit...