CD54HC165

CD54HC165 is 8-Bit Parallel-In/Serial-Out Shift Register manufactured by Texas Instruments.

Data sheet acquired from Harris Semiconductor SCHS156C

February 1998

- Revised October 2003

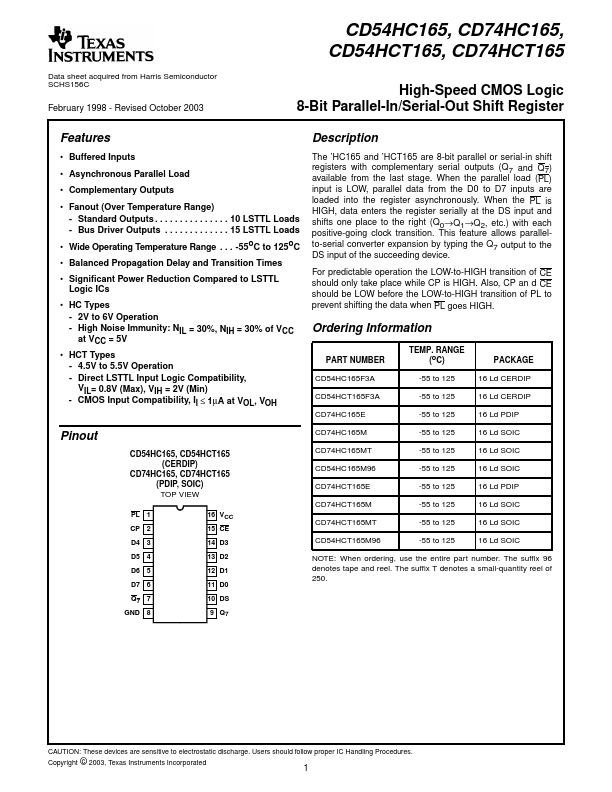

CD54HC165, CD74HC165, CD54HCT165, CD74HCT165

High-Speed CMOS Logic 8-Bit Parallel-In/Serial-Out Shift Register

[ /Title (CD74H C165, CD74H CT165) /Subject (High Speed CMOS Logic 8Bit Parallel-

Features

Description

- Buffered Inputs

- Asynchronous Parallel Load

- plementary Outputs

- Fanout (Over Temperature Range)

- Standard Outputs

- -

- 10 LSTTL Loads

- Bus Driver Outputs

- - . . . 15 LSTTL Loads

- Wide Operating Temperature Range . . . -55o C to 125o C

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction pared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

- HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic patibility, VIL= 0.8V (Max), VIH = 2V (Min)

- CMOS Input patibility, Il ≤ 1µA at VOL, VOH

The ’HC165 and ’HCT165 are 8-bit parallel or serial-in shift registers with plementary serial outputs (Q7 and Q7) available from the last stage. When the parallel load (PL) input is LOW, parallel data from the D0 to D7 inputs are loaded into the register asynchronously. When the PL is HIGH, data enters the register serially at the DS input and shifts one place to the right (Q0→Q1→Q2, etc.) with each positive-going clock transition. This feature allows parallelto-serial converter expansion by typing the Q7 output to the DS input of the succeeding device.

For predictable operation the LOW-to-HIGH transition of CE should only take place while CP is HIGH. Also, CP an d CE should be LOW before the LOW-to-HIGH transition of PL to prevent shifting the data when PL goes HIGH.

Ordering...