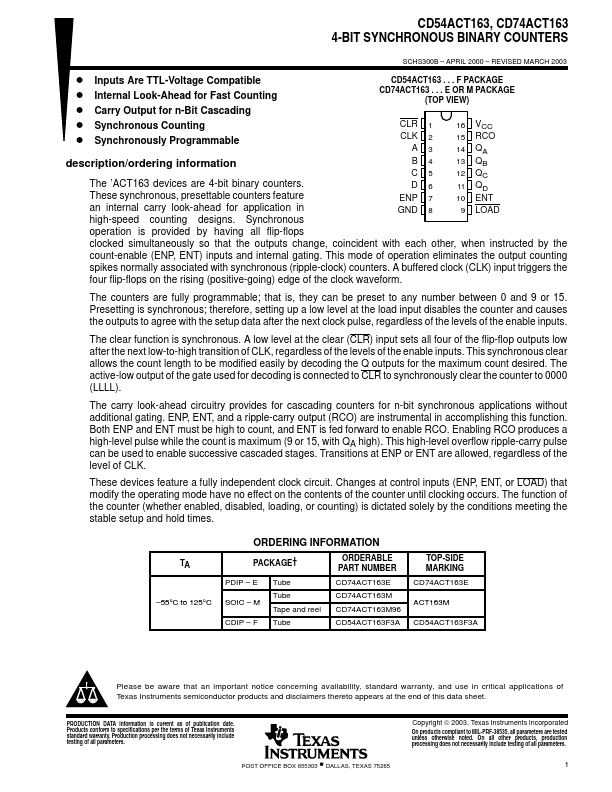

CD74ACT163

Key Features

- an internal carry look-ahead for application in high-speed counting designs

- This mode of operation eliminates the output counting spikes normally associated with synchronous (ripple-clock) counters

- A buffered clock (CLK) input triggers the four flip-flops on the rising (positive-going) edge of the clock waveform

- The clear function is synchronous

- This synchronous clear allows the count length to be modified easily by decoding the Q outputs for the maximum count desired

- The active-low output of the gate used for decoding is connected to CLR to synchronously clear the counter to 0000 (LLLL)

- The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without additional gating

- ENP, ENT, and a ripple-carry output (RCO) are instrumental in acplishing this function

- Both ENP and ENT must be high to count, and ENT is fed forward to enable RCO

- Enabling RCO produces a high-level pulse while the count is maximum (9 or 15, with QA high)