CD74HC138-Q1

CD74HC138-Q1 is 3- TO 8-LINE INVERTING DECODER/DEMULTIPLEXER manufactured by Texas Instruments.

HIGH-SPEED CMOS LOGIC

3- TO 8-LINE INVERTING DECODER/DEMULTIPLEXER

SCLS580A

- APRIL 2004

- REVISED APRIL 2008

D Qualified for Automotive Applications

D Significant Power Reduction pared to

D Select One of Eight Data Outputs Active

Low

D I/O Port or Memory Selector D Three Enable Inputs to Simplify Cascading

LSTTL Logic ICs

D 2-V to 6-V VCC Operation D High Noise Immunity; NIL or NIH = 30% of

VCC, VCC = 5 V

D Typical Propagation Delay of 13 ns at

VCC = 5 V, CL = 15 p F, TA = 255C

D Fanout (Over Temperature Range)

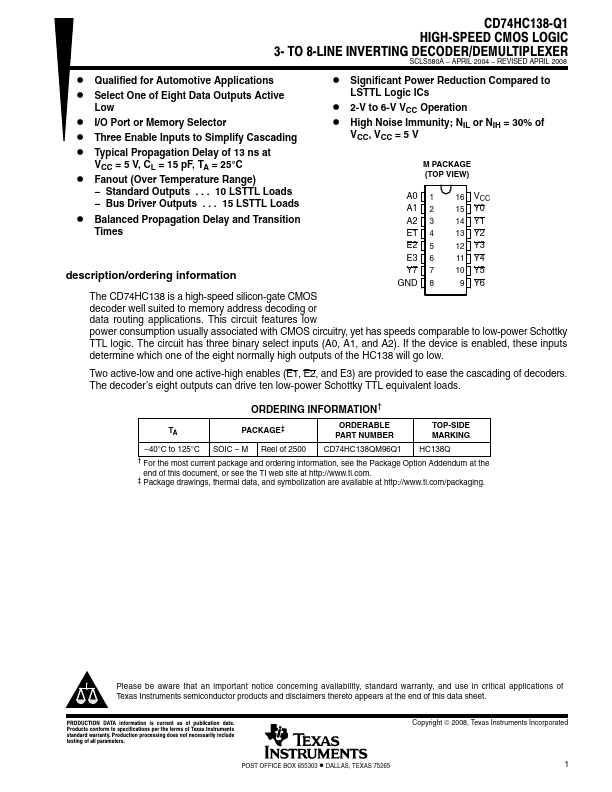

M PACKAGE (TOP VIEW)

- Standard Outputs . . . 10 LSTTL Loads

- Bus Driver Outputs . . . 15 LSTTL Loads

D Balanced Propagation Delay and Transition

Times

A0 1 A1 2 A2 3 E1 4

16 VCC 15 Y0 14 Y1 13 Y2

E2 5 12 Y3

E3 6

11 Y4 description/ordering information

Y7 7 GND 8

10 Y5 9 Y6

The CD74HC138 is a high-speed silicon-gate CMOS decoder well suited to memory address decoding or data routing applications. This circuit Features low power consumption usually associated with CMOS circuitry, yet has speeds parable to low-power Schottky

TTL logic. The circuit has three binary select inputs (A0, A1, and A2). If the device is enabled, these inputs determine which one of the eight normally high outputs of the HC138 will go...